电子技术论坛

信息来源: 时间:2021-4-23

MOS集成门电路布局-输出入及开关电路特性分析

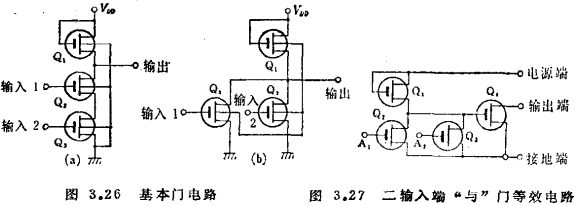

门电路可认为是倒相器电路的变形,基本上有图3.26所示的串联方式和并联方式。图(a)的电路为二输入端“或非”门(正逻辑)或为“与非”门(负逻辑)。一般,在这种电路方式中输出电压取决于两驱动管Q2、Q3导通电阻之和,为了得到与图(b)电路的相同特性,必须增加晶体管的面积,提高其跨导gm。这样做很不经济。所以实例很少。

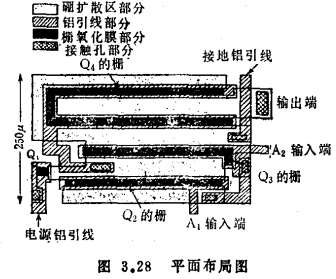

图(b)的电路为二输入端“与非”门(正逻辑)或为“或非”门(负逻辑)。MOS集成门电路。这种门电路的负载是与之连接的次级MOS晶体管的栅,为了缩短开关时间,则如3.3.1节倒相器电路中所述,须增大Q1的gm。而Von只取决于Q1、Q2的gm,因而Q2的面积也必然要增大。结果,在保证必要输入端数目的前提下,要增大晶体管的面积,就变得不经济了。MOS集成门电路。于是一般在门电路输出端加接一级倒相器电路。其等效电路如图3.27所示。此电路做成集成电路后的平面布局图如图3.28所示。

图上的黑条表示栅区,Q1的L为15μ,Q2~Q4的L为10μ。Q1为负载MOS晶体管,其W为15μ,而Q2以及Q3为驱动MOS晶体管,W为280μ。Q4要驱动与输出级连接的大负载电容,gm必须取得很大,所以该管的W要增加到735μ。由图3.28可知,构成源和漏区的硼扩散区部分、铝布线部分、栅氧化膜部分布局颇为得当,使整个图形的面积为最小。

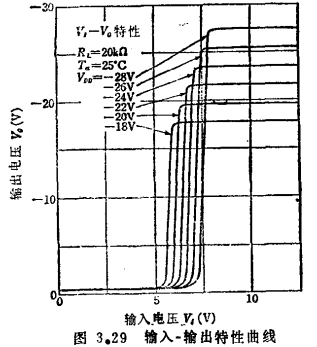

上述门电路的典型输入-输出特性如图3.29所示。

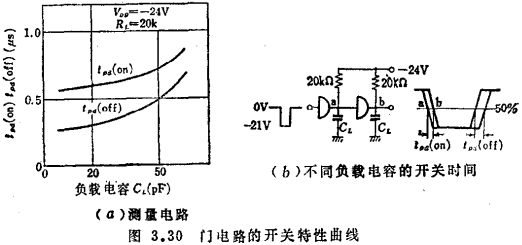

此图给出负载电阻为 ,参变量VDD在-28~-18V的范围内变化。开关时间是用图3.30(a)所示的电路测量的。MOS集成门电路。如前所述MOS电路的开关时间随负载电容而变,特性曲线的一个例子如图3.30(b)所示。

,参变量VDD在-28~-18V的范围内变化。开关时间是用图3.30(a)所示的电路测量的。MOS集成门电路。如前所述MOS电路的开关时间随负载电容而变,特性曲线的一个例子如图3.30(b)所示。

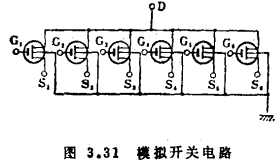

利用MOS晶体管有双向性的特点,可制成图3.31所示的用于模拟开关电路的门电路。

输入信号加到G1、G2、......G6上,假设源S1......S6为信号源,则输出端D就出现信号。如在栅上施加接近于源电压的电压,可使晶体管截止。因为MOS晶体管的截止特性极其良好,S/N比可以取得很高。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助