电子技术论坛

信息来源: 时间:2021-4-23

详解MOS集成倒相器电路及输入-输出特性分析

MOS集成倒相器电路

现在对所有电路的基础——倒相器加以说明,作为应用MOS集成电路的例子。为便于说明起见,设晶体管的形式为P沟道增强型,电压电平用正逻辑。

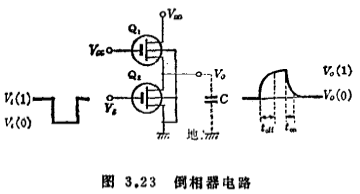

倒相器电路由跨导gm互不相同的两个晶体管Q1、Q2串联组成,因系集成电路,使用同一衬底,如图3.23所示。

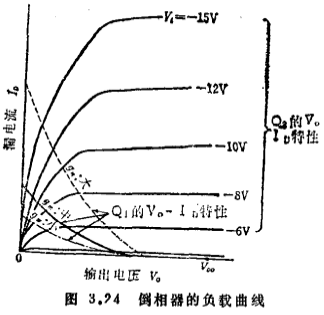

负载管Q1的栅上所加电压有VGG=VDD的情形,也有|VGG|>|VDD+Vth|的情形。前一种MOS负载管的工作状态为饱和型,此处除非特别加以说明,都是以VGG=VDD为对象。MOS集成倒相器电路。我们首先从基本特性来考虑。设漏电源电压为VDD(例如-24V),输入电压![]() 由零逐渐增加时,输出电压Vo可由图3.24的工作特性曲线求得。在图3.24中,输出电压Vo可由Q1的Vo-ID特性与Q2的Vo-ID特性的交点求得。如Q2的gm取恒定值,增大Q1的gm时,输出电压Vo向增高的方向移动,如图3.24的虚线所示。

由零逐渐增加时,输出电压Vo可由图3.24的工作特性曲线求得。在图3.24中,输出电压Vo可由Q1的Vo-ID特性与Q2的Vo-ID特性的交点求得。如Q2的gm取恒定值,增大Q1的gm时,输出电压Vo向增高的方向移动,如图3.24的虚线所示。

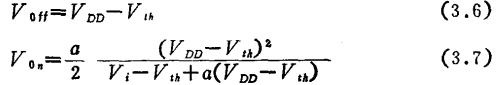

此时输出电压Voff、Von分别可用下两式表示。

式中1/a=L1W2/L2W1,

L1、L2分别为Q1、Q2的栅长度,

W1、W2分别为Q1、Q2的栅宽度,

Vth为Q1、Q2的阈值电压。

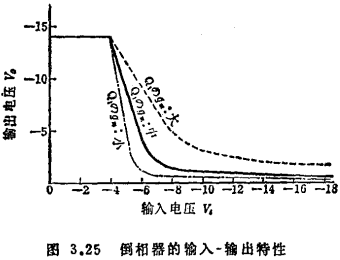

输出电压:Voff不等于VDD,而是比VDD低一个Vth的电平。这是MOS晶体管用作负载电阻时所不能避免的,因此在MOS集成电路中,漏电压应为比逻辑摆幅高出Vth的电压。MOS集成倒相器电路。另一方面,输出电压Von为VDD、Vi、Vth和a的函数,与gm的绝对值无关。图3.25是输出电压的典型特性。

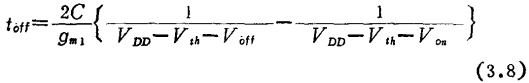

下面来考虑倒相器电路的开关时间。在MOS集成电路中,输入阻抗一般是容性的,倒相器电路的开关时间由负载电容的充放电时间决定。由于可动电荷是多数载流子,MOS晶体管本身的开关时间很快,可以忽略。Q2由导通到截止时,由于有来自Q1的充电电流流过负载电容C,输出电压逐渐增加,此时的开关时间toff如下式所示。

式中gm1为Q1的![]() ,C为次级栅的静电电容C1,Q1的源结电容与Q2的漏结电容C2之和。现假定次级也接入同样大小的倒相器电路(后述移位寄存器就是这样的例子),C1与C2都与Q2的gm2成正比,所以与Voffgm2/gm1=L1W2/L2W1=1/a成正比。MOS集成倒相器电路。另一方面,由截止到导通时,负载电容上积累的电荷通过Q2放电,一般Q2的gm比Q1大一个数量级以上,开关时间极快。

,C为次级栅的静电电容C1,Q1的源结电容与Q2的漏结电容C2之和。现假定次级也接入同样大小的倒相器电路(后述移位寄存器就是这样的例子),C1与C2都与Q2的gm2成正比,所以与Voffgm2/gm1=L1W2/L2W1=1/a成正比。MOS集成倒相器电路。另一方面,由截止到导通时,负载电容上积累的电荷通过Q2放电,一般Q2的gm比Q1大一个数量级以上,开关时间极快。

于是,MOS集成电路的基础——倒相器的输入——输出特性相器电路——的输入-输出特性以及开关特性都只和Q1、Q2的gm比值有关,与gm的绝对值无关。所以只要gm比值保持恒定,在光刻精度允许的范围内,晶体管的几何尺寸就可尽量缩小。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助