电子技术论坛

信息来源: 时间:2021-4-21

MOS集成电路的功能及工艺流程特性详解分析

(1)放大

MOS晶体管作为有源元件,本来就是用作放大元件的。在图3.15所示的互补型电路中,P沟道和N沟道晶体管互为有源元件和负载元件而工作,适用于重负载驱动和小功率电路。但与单沟道MOS集成电路相比,工艺流程复杂。

(2)负载

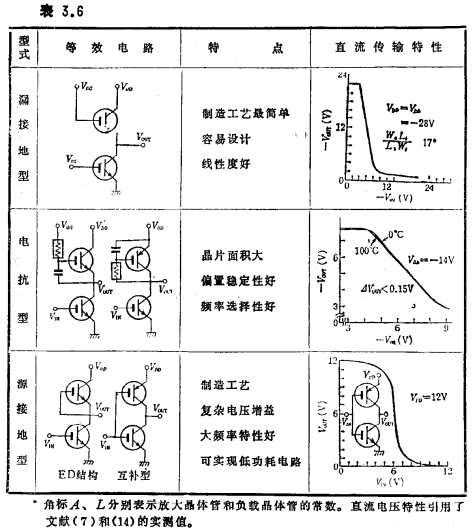

考虑其控制参数和芯片面积等单项功能,用MOS晶体管做负载要比扩散电阻负载有利。MOS晶体管负载利用了漏-源间的伏安特性,依栅接地的形式大体分为两种。MOS集成电路的功能表3.65)~7)上,除列出上述两种外,还加了一种兼具两者的优点的、可实现新功能的电抗型的负载形式。

表中所列的漏接地电路是目前最常用的形式,此时漏与栅均为交流接地。很多场合,为使电路简单起见,漏和栅接在一起,也就是采用直流连接形式。这种连接多用于增强型负载,由传输特性可以看到,输出电压的最大值一定在电源电压扣除 后的差值以下。也就是说电压利用率很差。为克服这一缺点,在特殊情形下,VG用另一电源。

后的差值以下。也就是说电压利用率很差。为克服这一缺点,在特殊情形下,VG用另一电源。

另一方面,在源接地型一栏内所示的两种电路,其负载都具有源接地的特性。在E-D结构的电路中,放大晶体管为增强型,负载晶体管为耗尽型。因呈现的是加上 大小的有效栅偏压的饱和区特性,故负载接近于恒流负载。MOS集成电路的功能从而最大输出电压几乎接近电源电压,对负载充电的电流也接近于恒流,故具有小功率、高速度的性质8)、9)。

大小的有效栅偏压的饱和区特性,故负载接近于恒流负载。MOS集成电路的功能从而最大输出电压几乎接近电源电压,对负载充电的电流也接近于恒流,故具有小功率、高速度的性质8)、9)。

互补型电路,与E-D结构有同样的效果,但由于负载可以互换,对降低功耗更为有利。也就是说,不管输入信号为1或0,总有一个晶体管处于截止状态,几乎没有电流流过两个晶体管,只是在 转换时,才流过对负载充电的电流。电抗型电路由漏接地电路和源接地电路组合而成。左侧的电路对直流为漏接地,对交流为源接地。直流传输特性就表示了这种情形。MOS集成电路的功能。若两个晶体管的尺寸大致相同,传输特性可以接近于45°,因而直流稳定度可以得到改善,又因为源系交流接地,可以获得增益。另外还可用于选频。左侧的图形为同样的电路用互补型构成的例子。

转换时,才流过对负载充电的电流。电抗型电路由漏接地电路和源接地电路组合而成。左侧的电路对直流为漏接地,对交流为源接地。直流传输特性就表示了这种情形。MOS集成电路的功能。若两个晶体管的尺寸大致相同,传输特性可以接近于45°,因而直流稳定度可以得到改善,又因为源系交流接地,可以获得增益。另外还可用于选频。左侧的图形为同样的电路用互补型构成的例子。

(3)传输门和模拟开关

由于对MOS晶体管而言可以对称地构成漏和源,漏和源是双向开关的信号端,栅可用作控制端。但在双极型晶体管中,因有作为控制信号的基极电流流入信号通路,故难以实现双向功能。但对MOS晶体管而言,双向开关可用作下面将要叙述的移位寄存器的传输门,存储器的写入和读出门等。又由于漏-源之间没有偏移电压,也可用作模拟开关以及斩波器。

(4)暂存

MOS晶体管的栅输入电阻极高,由输入电容和输入电阻决定的时间常数通常为几个毫秒。因此,在输入端加电压信号后再切断信号源时,在毫秒量级的时间内还有漏电流流过。可以像在移位寄存器中所用的那样,用于暂存信息。

(5)非易失性存储

所谓非易失性存储是切断电源后还可保存存储内容的功能。由于半导体单晶没有撤除外加电压后的滞后现象,就必须利用不是电路性的而是物理性的存储现象。MOS集成电路的功能。我们认为,如用简单的制造工艺能作成稳定的、好用的非易失性存储器,则半导体存储器的应用领域就会进一步扩大。这方面的研究工作正在进行之中。

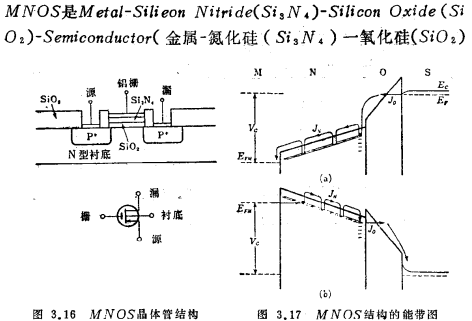

这类存储器之一种是利用被硅上绝缘膜内陷阱所俘获的电荷来控制硅表面势。最先做出的非易失性存储器是NMOS器件,如图3.16所示。图3.17是对该种器件的工作原理的说明。

(半导体)的缩写。如图3.17所示,利用流过Si3N4和SiO2的电流之差,可以改变对Si3N4和SiO2界面处陷阱充电的电荷。

当SiO2厚度约为100~50 时,如图3.17所示,流过SiO2的电流因隧道效应通过SiO2势垒的薄弱部分。当SiO2厚度在50

时,如图3.17所示,流过SiO2的电流因隧道效应通过SiO2势垒的薄弱部分。当SiO2厚度在50 以下时,直接的隧道电流增大。

以下时,直接的隧道电流增大。

作为这类非易失性存储器,以后发表了用Al2O3做绝缘体的MAS晶体管10),和用Al2O3~SiO2做绝缘体的MAOS晶体管11)。

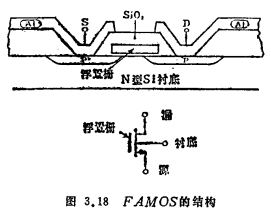

还有一种非易失性存储器,不是利用电荷穿越绝缘体的隧道现象,而是利用PN结雪崩击穿产生的高能电荷越过绝缘体势垒的现象。MOS集成电路的功能。图3.1812)是利用浮置栅的非易失性存储器,漏结雪崩击穿产生的电子越过SiO2注入到用多晶硅制造的浮置栅内,电子一经注入,就被高度绝缘的SiO2包围起来,所以能够长期保存。关于这种利用雪崩击穿的方式,还有利用注入电子来写入,以同样的方法利用注入空穴消去的电可改写存储器13)。

这种存储器的读出,在大多数场合都利用图3.16、图3.18所示的MOS晶体管结构,通过测量由表面势变化所产生的源-漏间的电流来进行的。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助