电子技术论坛

信息来源: 时间:2021-4-15

了解从逻辑设计来看的MOS集成电路功能知识分析

以采用集成电路(不限于MOS集成电路)为前提的电子仪器逻辑设计,与采用晶体管、二极管等所谓分立元件时相比,要受很大的限制。逻辑设计的最终目的在于降低成本。仅仅根据这一点,也要从不同于分立元件的角度来进行逻辑设计。设计时必须注意的问题是基本的逻辑构成方式和相同逻辑功能的数目。MOS逻辑集成电路。尤其在使用MOS集成电路时,前者(基本的逻辑构成方式)将在整机设计中占极大比重。以下对此加以分析。

所谓基本的逻辑构成方式,有以门为主体构成逻辑的方法和以触发器为主体构成的方法。过去在使用分立元件和双极型集成电路的场合,曾采用以门为主体的方式,但对MOS集成电路来说,使用条件就大不相同。MOS逻辑集成电路。也就是说,MOS集成电路与分立元件和双极型集成电路相比,其特点为触发器的价格比门电路要便宜。这说明MOS集成电路的功能效率甚优,构成逻辑电路所需的元件(MOS晶体管)较少,例如在12引线的TO-5管壳内通常可封装4枚输入端和输出端数目少的D型触发器。因此,在采用以门或触发器为单元的集成电路组成电子仪器时,利用MOS集成电路所具有的这种特点,多用触发器而少用门电路。

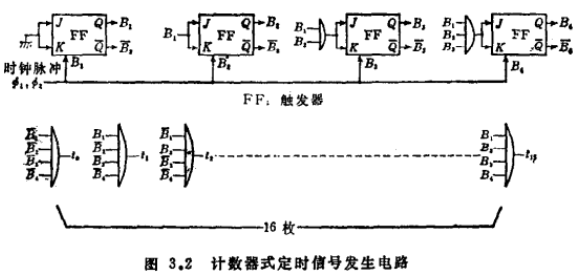

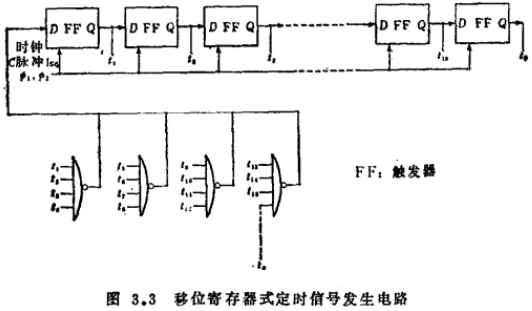

此处,以串行数字计算机中不可缺少的定时信号发生器为例加以说明。图3.2是过去所用的,由二进制计数器的堆积与译码门电路构成的电路,包含两个J-K触发器的集成电路需要2枚,包含两个四输入端“与”门的集成电路需要8枚,包含三个三输入端“与”门的集成电路需要1枚,总计需集成电路11枚。相比之下,如采用图3.3所示的具有修正错误能力的环形计数器,则需要包含四个D型触发器的集成电路4枚,四输入端“与非”门集成电路2枚,总共要用6枚集成电路构成。可见,有必要研究适应MOS集成电路的基本逻辑电路结构和控制方式。

下面我们来研究采用集成电路时必然要碰到的问题,即相同逻辑功能的数目问题。图3.3的实线部分是16进制环形计数器。我们看一看17进制环形计数器又将如何?虽然也可以简单地再加接一个D型触发器,但在另一方面会产生问题。1枚集成电路的同步信号是共同的,所以加接的集成电路内4个触发器的同步信号也是相同的,假如用这一同步信号驱动的触发器没有别的什么用途,剩下的3个触发器就完全是多余的了。MOS逻辑集成电路。在这种情形下就要研究一下不加接集成电路构成17进制计数器的方法,同时要研究在这种条件下使用3个触发器简化其它逻辑的问题。图3.3的虚线部分给出用四输入端“与非”门的四个输入端构成17进制计数器的方法。对构成方法的研究是十分必要的,因其直接影响成本。当然,这类问题并不限于触发器,也适用于倒相器和门电路。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助