电子技术论坛

信息来源: 时间:2021-4-13

MOS场效应晶体管弱电压放大电路特性电压等关系分析

如信号源电阻Rs为100MΩ,Ig的变化部份为1×10-14A,由式(2.154)可知栅电流Ig产生的漂移电压为Ig的变化部份与信号源电阻的乘积,即1x10-14×108Ω=1μV。从而Rg若在数十MΩ以下,与电压性漂移υd相比,Id可以忽略。

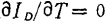

由式(2.144’)取 ,可求得

,可求得 ,υd的大小就等于

,υd的大小就等于 。如将式(2.144')对温度微分,得

。如将式(2.144')对温度微分,得

式中

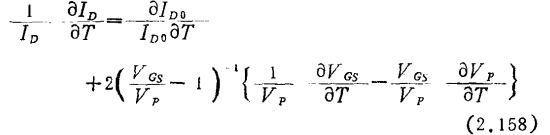

其中q为电子电荷量(1.6×10-18库仑),Cg为单位沟道长度的栅电容,μ为载流子迁移率,L为沟道长度,nss为SiO2~Si界面的载流子浓度。MOS场效应晶体管弱电压放大电路。其中,随温度变化的主要因素是μ和nss,所以如将式(2.159)代入式(2.158)并使之等于零,则得换算到输入端的温度漂移

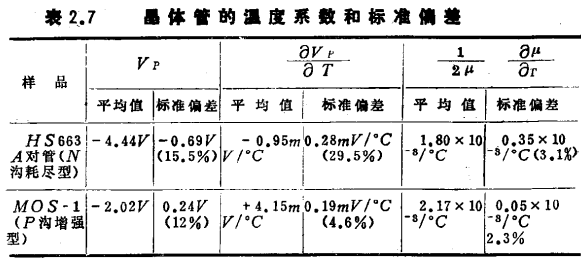

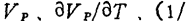

一般在SiO2~Si界面,电子密度有随温度成正比例增加而载流子迁移率有随温度成反比例减少的趋势。表2.7给出作者等试制的MOS场效应晶体管温度系数的平均值及其标准偏差的大小。在N沟道耗尽型中载流子为电子,其密度与温度成正比例增加,所以Vp随温度成正比例增加;

在p型沟道中载流子为空穴,此空穴被nss的随温度的增加部分所抵销,所以VT随温度成反比例减少。另外,在N型沟道,VGS-Vp>0;在P型沟道,VGS-Vp<0,式(2.160)右边的第一项和第二项具有互相抵销的极性,当时温度漂移为零。

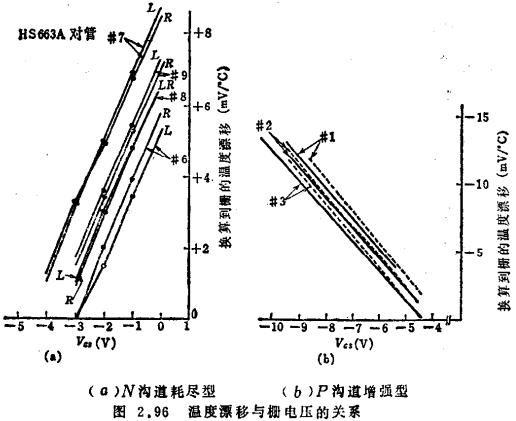

图2.96是这种温度漂移与VGS的关系。图2.96(a)、(b)都表明在 的范围内温度漂移υd为零。从式(2.160)还知道,υd与VGS(栅直流偏压)成正比。

的范围内温度漂移υd为零。从式(2.160)还知道,υd与VGS(栅直流偏压)成正比。

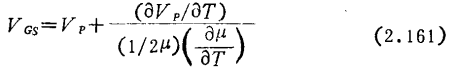

也可以用将VGS调整到式(2.161)所示的值的方法来设计稳定的直流放大电路,但实际上考虑到

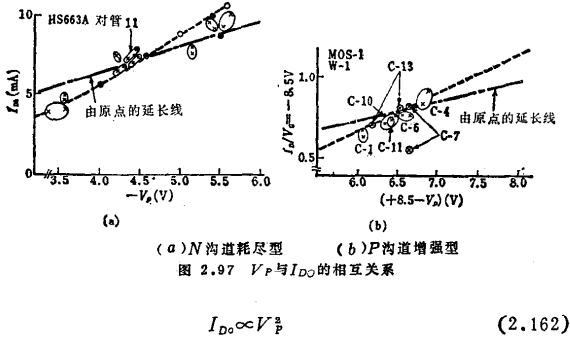

等均有偏差,调节起来颇为麻烦,所以并不实用。实用的低漂移电路仍然是差分放大电路。此时,漂移的上限受器件特性偏差的制约。MOS场效应晶体管弱电压放大电路。静态特性的偏差可由IDO和Vp的偏差看出。由式(2.159)可以看出形成这些偏差的原因有μ、nss、L、Cg等。实测的IDO与Vp是相关的,如图2.97所示,大致有如下关系:

等均有偏差,调节起来颇为麻烦,所以并不实用。实用的低漂移电路仍然是差分放大电路。此时,漂移的上限受器件特性偏差的制约。MOS场效应晶体管弱电压放大电路。静态特性的偏差可由IDO和Vp的偏差看出。由式(2.159)可以看出形成这些偏差的原因有μ、nss、L、Cg等。实测的IDO与Vp是相关的,如图2.97所示,大致有如下关系:

从而静态特性偏差的主要原因在于nss。

另一方面,差分放大电路的温度漂移为两个器件υd之差,可由式(2.163)给出。

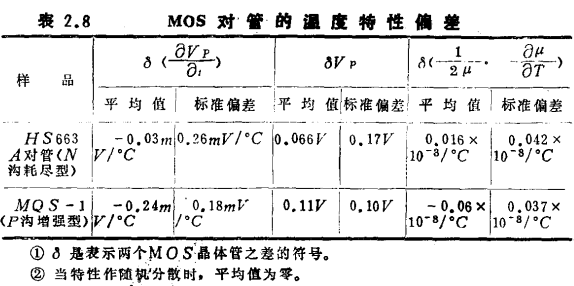

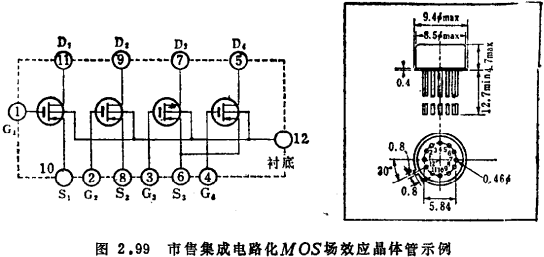

经笔者等的研究,发现:对集成电路化的对管来说,各漂移项的大小大致相等,各项之间也没有相关关系(参见表2.8)。

总的温度漂移如表2.9所示,具有

集成电路化对管的υd≌0.1~0.25(mV/℃)(2.164)的关系。这种漂移电平与差分放大用的对管化(集成电路化)双极型晶体管和结型场效应晶体管的漂移电平相比要大得多。MOS场效应晶体管弱电压放大电路。但是,如采用稳定的批量生产工艺流程,器件间隔又设计得尽可能地窄,MOS对管的漂移电平大概可改善到0.1mV/℃以下,平均达到0.05mV/℃左右。

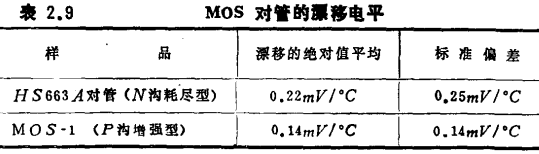

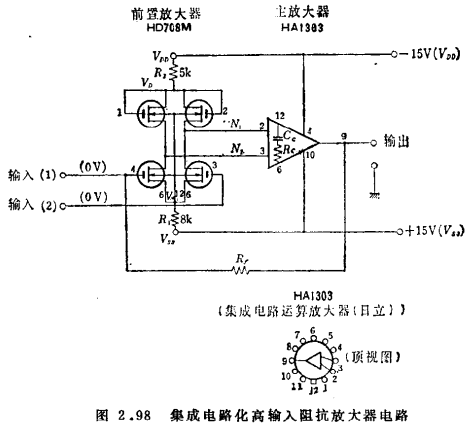

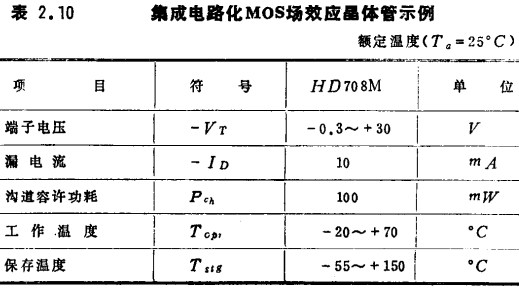

图2.98是采用MOS场效应晶体管集成电器器件的高输入阻抗放大器的例子。此器件→集成电路化的四个P沟道增强型MOS场效应晶体管构成,本来是作为台式计算机中的逻辑元件而研制的品种(参见图2.99、表2.10)。

在前置放大器,HD708M中的两个管子用作差分放大,另外两管用作负载,构成级联放大电路。今设四个MOS场效应晶体管的特性相等,其跨导为gm,因负载器件的电阻值为1/gm,所以前置放大电路的电压增益G1为

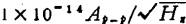

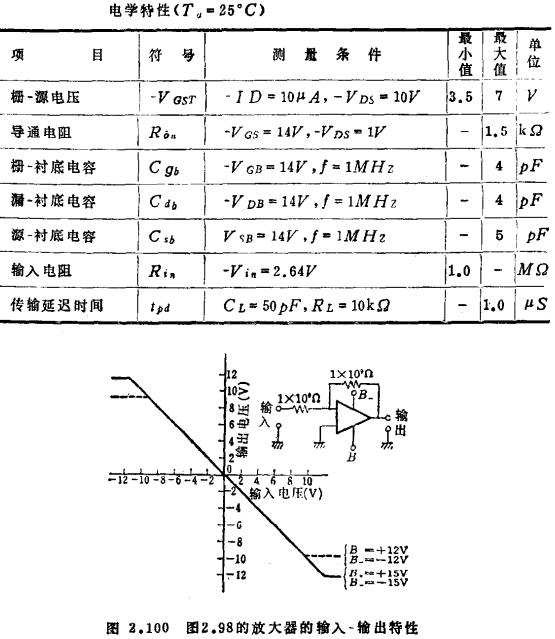

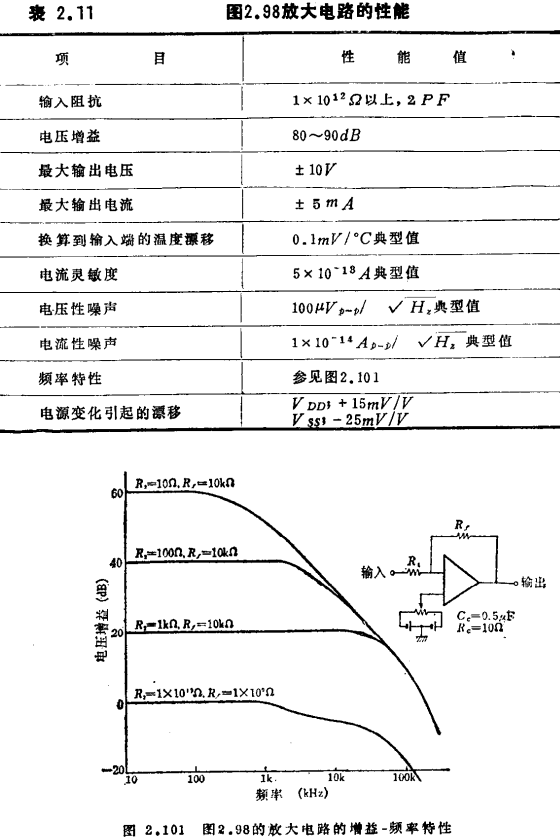

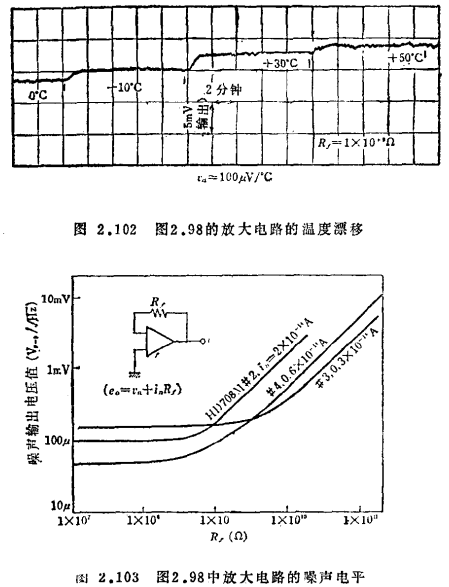

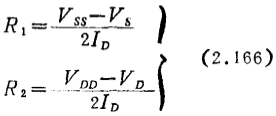

也就是说,在这里前置放大电路可用作阻抗变换器。各MOS场效应晶体管的栅电极与硅衬底间连接有用集成电路方法制成的齐纳二极管,可防止静电感应、带电等引起的栅损坏和特性变化。但另一方面,由于齐纳二极管有漏泄电流,致使输入阻抗和偏移电流、电流性噪声等要增大一些。表2.11是其综合性能。图2.100是输入-输出特性,图2.101是增益-频率特性图2.102是温度漂移的例子,图2.103给出噪声电压与负反馈电阻Rf的关系。MOS场效应晶体管弱电压放大电路。在2.2.1节的式(2.143’),如设Rs=Rf,由测量结果可分离出电压性噪声 和电流性噪声in,分别为

和电流性噪声in,分别为

和

和 。

。

这种电路的设计要点是,因主放大电路中集成电路运算放大器的输入直流偏压为0V,所以前置放大器输出直流电压也应设置在0V附近。为使输入电压为零时,前置放大器的输出电压亦大致为零,图2.98的R1和R2应根据电源电压适当设置。

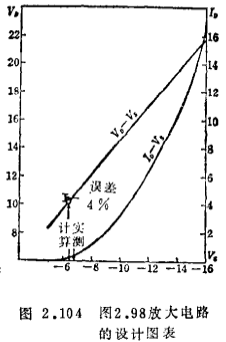

HD708M的硅衬底为N型。因为此N型衬底与漏和源之间形成的P-N结不处于正向偏置,N型衬底应连接到HD708M最正的电位点,即图2.98的Vs点上。如衬底电位不同,当然ID~VGS特性要受衬底电位的影响而发生变化。此处为使设计方便起见,将衬底电位换算成栅电压VGS,其换算系数由实验求得,并作出图2.104所示的设计图表。此图的用法是,首先决定直流工作电流ID,由ID-Is曲线求得s,再由Vs-VD曲线求得VD。当电源电压Vss、VDD高于Vs、VD时,在各自的支路中插入降压电阻R1、R2:

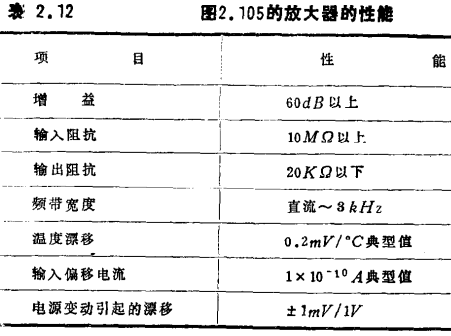

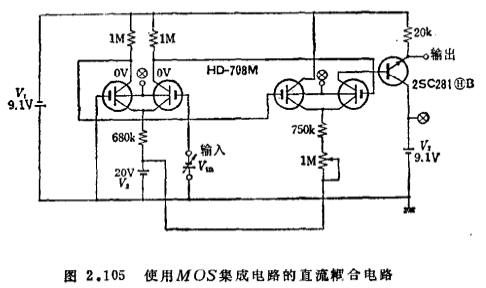

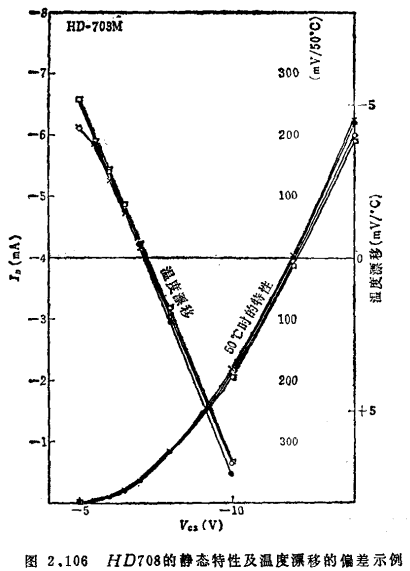

图2.105是使用MOS集成电路器件HD708M的其它例子。此处因一块HD708M集成电路能得到60dB以上的增益,所以整个电路按低电平下大负载进行设计。图2.106是同一集成电路内的四个管子的静态特性和温度漂移的偏差。表2.12是这种放大器的性能表。

与表2.11相比输入偏移电流大,是因为硅衬底与栅之间的电压较大,栅保护用齐纳二极管漏泄电流增大的缘故。

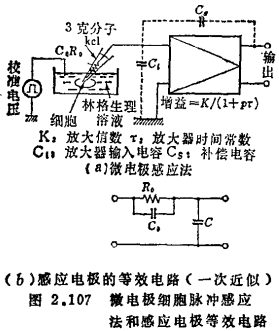

有时要测量具有极高内阻的信号源的电压。例如PH(酸碱度)计、压电计(晶体传声器及其它、采用强电介质的各种探测器及其它)等即是。在这种情况下应使放大器的输入阻抗大于信号源阻抗,所以多采用图2.86(b)的电路结构。图2.107(a)是要求高输入阻抗的另一例子58)。生物细胞发生的脉冲电压(-40~100mV)可用直径1μ左右充满电解液的管状玻璃电极插入细胞内部进行探测。MOS场效应晶体管弱电压放大电路。因脉冲宽度为几ms左右,为了不失真地探测并放大这种脉冲电压,要求有从直流到几kHz以上的频带宽度。但这种玻璃电极的内阻约为100MΩ,而且应该观察的脉冲宽度为几毫秒,所以放大器必须是高输入阻抗型直流放大器。

另一方面,输入端的微小杂散电容会使感应脉冲的波形造成显著失真,因而这种输入端电容,包括玻璃电极电容、放大器输入电容在内,应在0.1pF以下。可用正反馈形成的负电容补偿掉上述电容。其补偿条件是,换算到放大器输入端的负电容(K-1)Cs应等于电极电容C与放大器输入电容Ci之和。

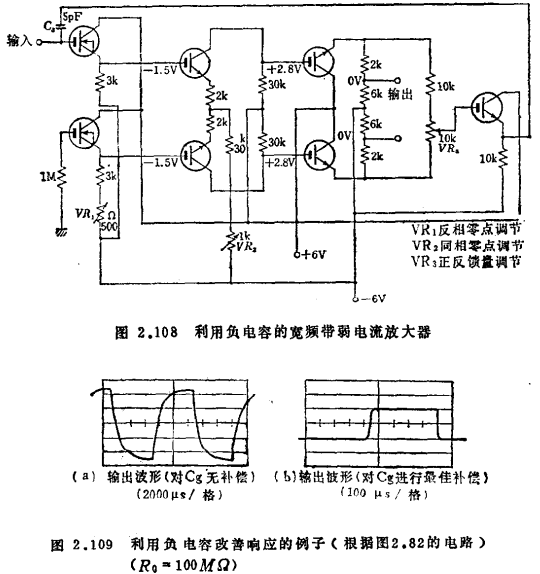

然而若正反馈补偿过量,放大器就变得不稳定(产生振荡)。图2.108是试制的放大器电路。为了减少输入电容,降低由输入端到细胞的漏泄电流,前级采用MOS场效应晶体管,其增益由源跟随器电路来稳定。第二级是NPN晶体管的差分放大电路,各发射极接入2kΩ的电阻。第三级是发射极跟随器的差分电路。于是,为了使增益充分稳定,在输出端和输入端之间接上绝缘性能良好的聚苯乙烯电容器(5pF)施加正反馈。如补偿到最佳状态,原来的上升时间可改善到10μS左右,改善程度约为200倍(参见图2.109)。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助