电子技术论坛

信息来源: 时间:2021-3-3

硅栅CMOS工艺流程框图及等平面隔离硅栅CMOS工艺步骤

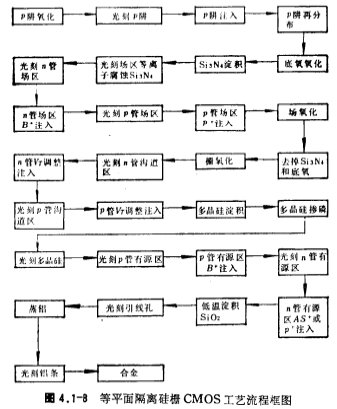

1、硅栅CMOS工艺流程框图

虽级然铝栅CMOS工艺比较成熟、稳定,但由于存在着较大的栅漏、栅源交叠寄生电容,使电路速度较慢,再加上n+、p+沟道截止环占用面积较大,集成度做不高等问题,因此,在等平面隔离n沟硅棚工艺的基础上发展了等平面隔离硅栅 CMOS工艺。此种工艺虽然流程较长,但缩小了CMOS电路的面积,改进了电路的速度性能,且版图设计筒单而规则,宜于用计算机辅助制版,因而已成为当前MOS工艺中的主要工艺。

等平面隔离硅棚CMOS的工艺流程框图如图4.1-8所示。

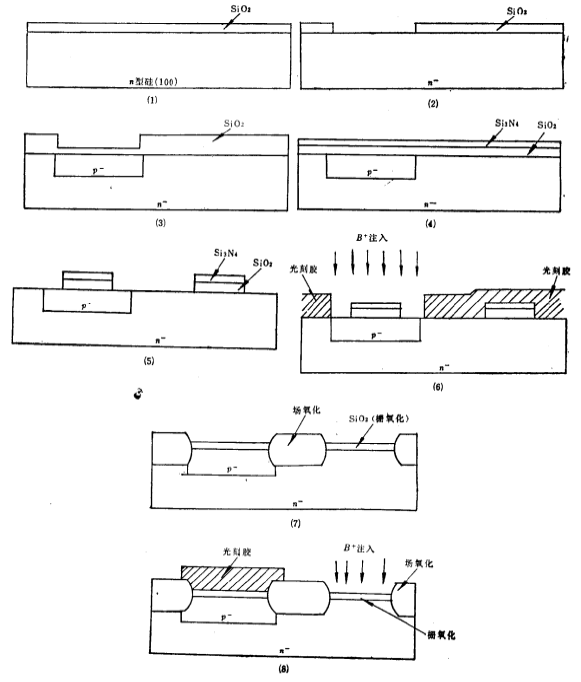

等平面隔离硅栅CMOS工艺流程如图4.1-9所示。

2、工艺流程步骤

结合图4.1-8和图4.1-9,我们简要介绍硅栅CMOS的工艺流程步骤;

(1)预氧化

在n型(100)硅片上进行第一步热氧化,作为P阱注入和再分布的掩蔽。

(2)P阱光刻

(3)P阱硼离子注入和P阱再分布

P阱注入剂量对n沟MOS管的阀值电压 有直接的影响,必须根据电路对

有直接的影响,必须根据电路对 的要求来决定注入剂量,一般为1013/厘米2左右。

的要求来决定注入剂量,一般为1013/厘米2左右。

(4)底氧氧化和Si3N4淀积

首先去掉预氧化层,然后进行底氧化和Si3N4淀积,以作为场氧化的掩蔽。

(5)光刻场区

需要场氧化的地方,通过光刻和等离子腐蚀方法去除该处的Si3N4。

(6)n沟场注入光刻

为提高n沟场区的场开启电压VTF,对n沟场区必须进行硼注入,由于有源区部分已有Si3N4掩蔽,硼离子不会注入进去,因此场注入光刻版与P阱版形状相同,只要把P阱外的区域用光刻胶掩蔽起来即可。硅栅CMOS工艺。n沟场注入的剂量由VTF决定,一般为1013/厘米数量级,注入能量要恰当,能量太低,在场氧化时,容易进入到场氧化层中去;能量太高会穿过Si3N4到有源区,以致影响MOS场效应管的 场注入后进行去胶,去胶后此道光刻图形不再保留。

场注入后进行去胶,去胶后此道光刻图形不再保留。

(7)场氧化及去除Si3N4

通过较长时间的湿氧氧化,在场区生长一层约1微米的氧化层,以提高场开启电压。场氧化完毕后,用热磷酸去除Si3N4。

(8)棚氧化和VTF调整B+注入

去掉Si3N4下的底氧,重新进行清洁氧化,在MOS管栅区上长出一层薄栅氧化感;然后进行 调整光刻。硅栅CMOS工艺。

调整光刻。硅栅CMOS工艺。 调整光刻,只要把n沟MOS管区用光刻胶掩蔽即可,因此可以用P阱的反版,此道光刻不需要腐蚀,去胶后图形不保留。

调整光刻,只要把n沟MOS管区用光刻胶掩蔽即可,因此可以用P阱的反版,此道光刻不需要腐蚀,去胶后图形不保留。

VTF调整用离子注入硼来实现,注入剂量约1011/厘米2数量级,能量可以较低,只要能穿过栅氧化层即可。

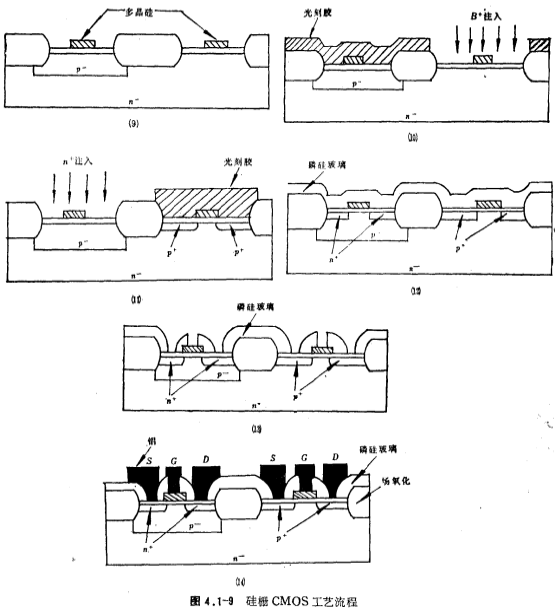

(9)多晶硅淀积、多晶硅掺杂和多晶硅光刻

用低压化学气相淀积(LPCVD)方法在整个硅片表面淀积一层多晶硅,然后进行磷扩散,使多晶硅的R□≈30欧姆/方左右,再进行多晶硅光刻,把MOS场效应管栅区上的多晶硅及用作连线用的多晶硅保留,其他地方的多晶硅用等离子刻蚀法去除,

(10)P+区光刻,P+区硼注入

为了进行P+区(P沟漏源区和P阱中的P+环)的硼注入,必须把n+区用光刻胶掩蔽起长,至于场区则有厚的场氧化层掩蔽,MOS管的沟道区有多晶硅掩蔽,可以不必考虑再加作什么掩蔽物。光刻时不必进行腐蚀,即可进行P+区硼离子注入,为减少P沟漏源区的电阻,注人剂量要稍大,一般为1014~1016/厘米2,注入完毕即行去胶,去胶后图形不保留。

(11)n+区光刻,n+区磷(或砷)注入

在进行n+区(n沟漏源区和n-硅衬底中的n+电极)光刻时,必须把P+区用光刻胶掩能起来,为简单起见,只要用P+区光刻的反版即可。硅栅CMOS工艺。光刻后同样进行n+离子注入,随后去胶,图形不保留。

(12)磷硅玻璃淀积和漏源再分布

用低温淀积方法在硅片上淀积一层磷硅玻璃,使高台阶的坡度变小,以利于铝条爬高坡时不致断裂:同时进行漏源再分布。

(13)引线孔光刻

(14)铝淀积、光刻铝条、钝化和钝化版光刻

与其他电路的工艺一样进行铝淀积,铝条光刻和钝化,钝化版光刻。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助