电子技术论坛

信息来源: 时间:2021-3-2

CMOS铝栅-硅栅等平面隔离典型工艺分布流程详解

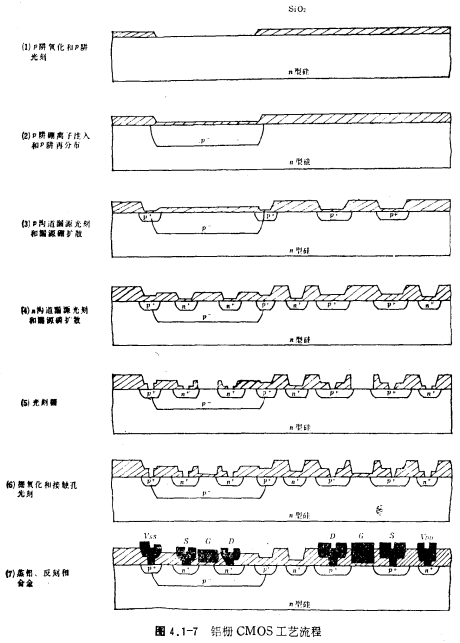

铝栅CMOS的流程如图4.1-7所示。简单说明如下:

1、p阱氧化和p阱光刻

在n型硅片上热生长一层SiO2,作为P阱离子注入的掩蔽层,氧化层厚度根据离子注入能量、剂量以及p阱再分布温度和时间来定,一般要求在5000埃以上。然后进行光刻,把P阱区的氧化层腐蚀掉。

2、P阱硼离子注入和再分布

P阱是CMOS电路中n沟MOS管的衬底,P阱表面杂质浓度的大小,直接影响着n沟MOS场效应管的阈值电压,因此必须严格控制P阱离子注入的能量,剂量及随后进行的P阱再分布条件,由于P阱的杂质浓度较淡(表面浓度约1015/厘米3,随着扩散深度加大,浓度越来越淡),n沟漏源区与P阱之间的p-n结耗尽层宽度就比较宽,因此P阱深度不能太浅,以防止n沟漏源区与n-硅衬底之间的穿通,并避免寄生npn双极型晶体管的β过大。一般P阱深度约8~10微米,再分布温度为1200℃,时间为10小时左右。

在P阱再分布的同时,也进行着热氧化,以作为下道p+、n-扩散时的掩蔽。在热氧化过程中,必然会有很多B+离子跑到SiO2中去,因此离子注入的剂量必须适当大一些,定量分析可由计算机工艺模拟进行计算,一般取1013/厘米2数量级。

3、P沟道漏源光刻和漏源硼扩散

在P沟道漏源光刻的同时,把NMOS管周围的P+沟道截止环同时刻出,以便一起进行P+硼扩散。在硼扩散的同时还进行热氧化,以作为p+区上的保护层及下一道n+扩散的掩蔽。

4、n沟道漏源光刻和漏源磷扩散

在n沟道漏源光刻的同时,把PMOS晶体管周围的n+沟道截止环同时刻出,以便一起进行n+磷扩散。在磷扩散的同时还进行热氧化,以作为n+区上的保护层。

5、光刻栅

在刻出MOS管栅区的同时,把引线孔也刻出,以便于以后的引线孔腐蚀。

6、栅氧化和接触孔光刻

用清洁氧化工艺在硅片上生长一层优质的薄栅氧化层,然后进行引线孔光刻。

7、蒸铝反刻和合金

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助