电子技术论坛

信息来源: 时间:2021-2-26

CMOS运放直流工作-直流转换-交流小信号-瞬态特性分析

对一般的运放而言,计算机辅助模拟主要了解以下几项工作特性。

1、直流工作点分析

此项分析的目的是为了模拟运放直流工作状态,确认电路各工作点是否符合设计要求。通常,把输入端均接地,此时,出现在输出端的电压是由运放的失调所致。直流分析可用。OP语句完成。

2、直流转换待性

用.DC语句或TRAN语句(用.TRAN时,要在输入端加一个上升时间足够长的脉冲源或分段线性源)对整个电压范围进行扫描,以此确定运放的动态范围及共模输入范围。

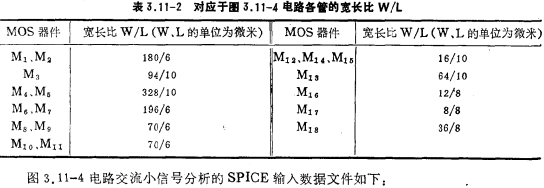

3、交流小信号分析

交流小信号分析主要完成运放的频域分析。一般在输入端加一交流小信号(其值足够小,而不致引起输出进入饱和区),并打印输出端电压的幅值及相位,即可得到运放的幅度频率(简称幅频)特性和相位频率(简称相频)特性。用.AC及.PRINT语句完成这项分析。

4、瞬态分析

把运放倒相输入端与输出端短接,即构成跟随器形式。在同相输入端加上升时间足够短的一脉冲源或分段线性源,打印输出电压,可获得压摆率、建立时间等瞬态响应参数。瞬态分析由.TRAN和.PRINT完成。

5、共模抑制和电源抑制特性

共模抑制比和电源抑制比的测量是交流小信号分析的一部分。在输入端分别加差模和共模小信号,把差模放大倍数与共模放大倍数相除,即为共模抑制比(CMRR)。如把输入端接地,并在正或负电源上叠加一交流小信号,在输出端得到的放大倍数与差模放大倍数相除,就是正或负电源的电源抑制比(SPRR)。遗憾的是,SPICE没有把输出结果进行相除的运算功能。因此,如需绘制CMRR和SPRR曲线,用户只能自己对输出结果进行处理。

下面用两个实例对CMOS运放的模拟作简要的说明。

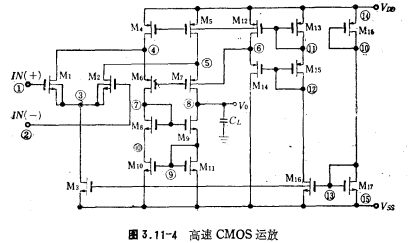

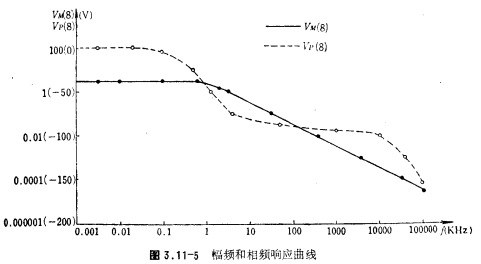

【例1】图3.11-4所示的是一个共源共栅型结构的高速CMOS运放,图中管子的宽长比列于表3.11-2。

SPICE规定接地节点编号为零。在上面的模型语句中,参数“LAMBDA”反应了MOS器件的沟道调制效应。通常,其值是这样凭经验给出的:当沟道长为10微米左右时,LAMBDA值取0.02,而当沟道长小于6微米大于3微米时,其值为0.03。LAMDA的缺省值为零,文件中.AC指定在1毫伏小信号输入时,从1赫兹开始至100兆赫每十倍频程分桥10点。

SPICE在作交流分析前自动进行的直流工作点分析结果(各节点电压)如下:

(1)0.0000 (2)0.0000 (3)-1.5451 (4)3.3680 (5)3.3680

(6)1.6587 (7)-0.0049 (8)-0.0049 (9)-3.1134 (10)-3.1134

(11)2.9756 (12)-0.7417 (13)-1.8948 (14)5.0000 (15)-5.0000

从中可以看出,输出节点8的电压接近于零,亦即电路失调电压很小。按.PLOT语句要求绘制的相频响应和幅频响应曲线如图3.11-5所示,曲线对应的单位增益频率约为3.2兆赫,开环增益为3.23×103倍。

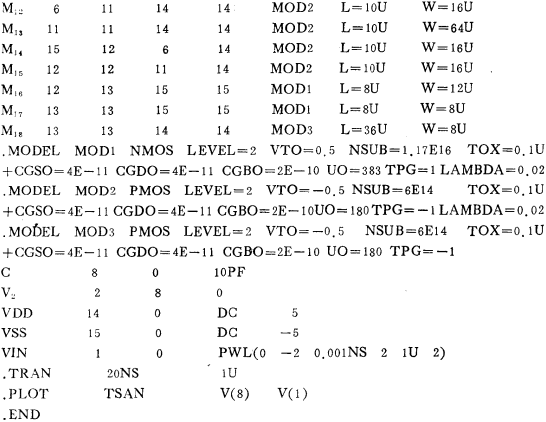

对运放进行瞬态分析的输入文件如下:

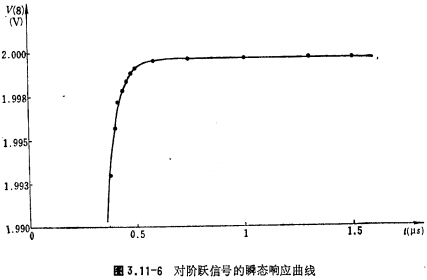

SPICE不允许有零值电阻存在,因此,短路一般均用零值独立源来表示。如上面文件中的电压源V2即表示节点2与8是短路的。输入电压源VIN采用分段线性源PWL来描述一个从0跳变至2伏,上升时间为0.001纳秒的脉冲信号,并从0开始至1微秒,每隔20纳秒分析一点。输出曲线如图3.11-6所示。

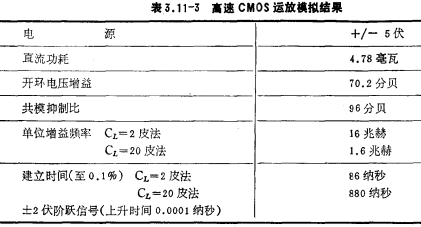

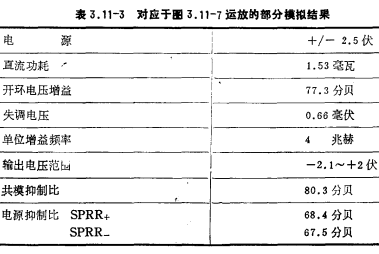

由曲线可知,运放建立时间约为430纳秒。运放的其他一些参数的模拟结果已列于表3.11-3中

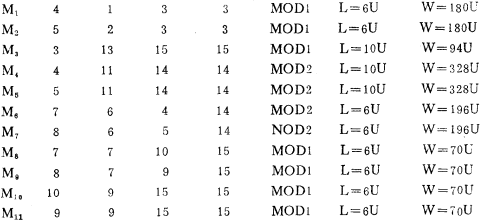

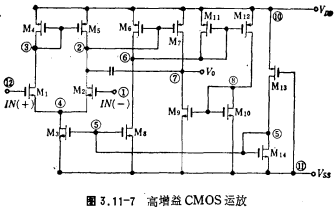

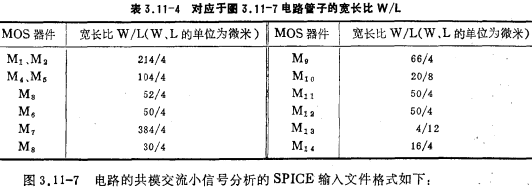

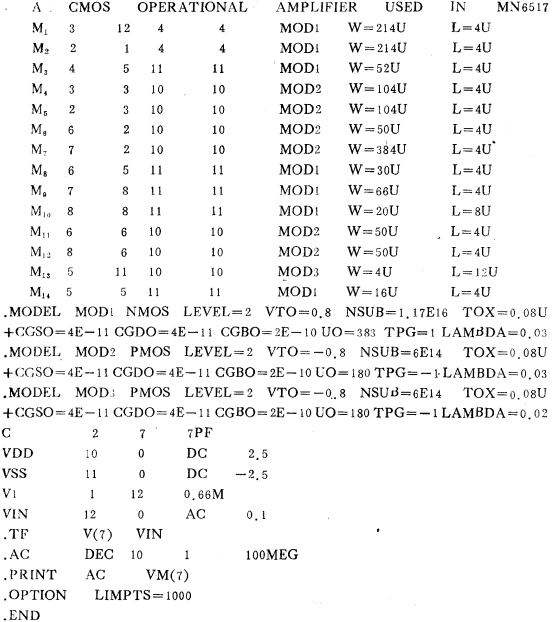

【例2】图3.11-7所示的是一个用于开关电容滤波器6517中的高增益CMOS运放,电路中各管的宽长比列于表3.11-4。

上面输入数据文件中电压源V1是加在运放输入端的失调电压。在运放设计中,由于参数的近似估算,运放的直流工作点模拟结果常出现很大的失调电压,使得运放处于不正常的工作状态,为了继续模拟运放的稳态和瞬态特性,”通常采用两种方法,一种是在输入端加一适当的失调电压源,正好抵消电路本身的失调,使电路恢复到正常的工作状态,即输入为零时,输出亦为零。另一种方法是加适当的反馈电阻,构成一负反馈放大器,先分析负反馈放大器的各种特性,然后,折算为运放开环参数。

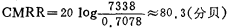

从模拟输出结果可知,运放共模放大倍数为0.7078倍。把上述文件中的负输入端接地,而正输入端接1毫伏交流小信号,则输出即为运放的差模频率响应特性。由模拟结果得知,开环放大倍数为7338倍。从而共模抑制比为

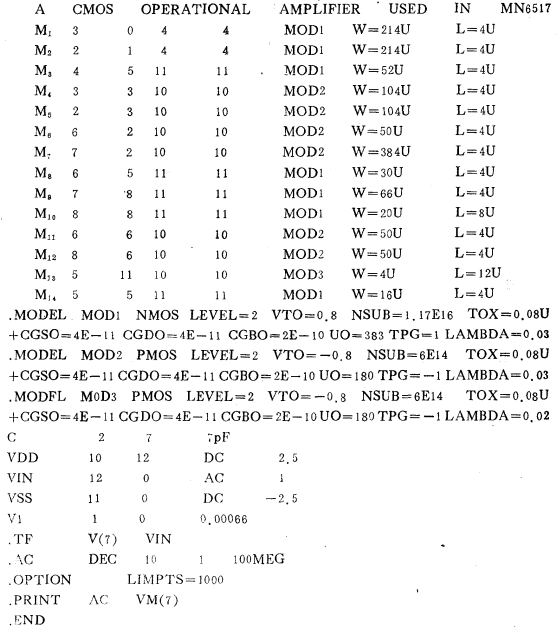

下面的输入文件是模拟运放的电源抑制能力。

运放的两个输入端之间接一失调电压,然后接地,并在正电源节点10上面叠加一个交流小信号于直流电源之上,分析并打印输出端7对输入的响应。

模拟结果表明,对正电源上所叠加的小信号,其放大倍数为2.8倍,由此求得运放对正电源的电源抑制比为

运放对负电源的电源抑制比可用相同方法得出。运放部分模拟结果列于表3.11-3中。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助