电子技术论坛

信息来源: 时间:2021-1-28

CMOS运算放大器的电源抑制比(PSRR)详细和分析

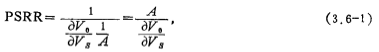

电源抑制比(PSRR)定义为,电源电压变化所对应的输出电压变化折算到输入端的值之比,即

式中A 为运放的开环增益,Vs为电源电压,Vo为输出电压。

近年来,MOS大规模集成电路中既有模拟电路又有数字电路,即模拟电路与数字电路做在同一芯片上,这样数字电路的脉冲信号往往通过电源对模拟电路(如运放电路)产生干扰,此干扰信号使得运放在没有信号输入的情况下产生一个输出信号,从而影响了运放电路的正常工作。在单片式运放电路中,通过采用退耦或与数字电路的电源分开等方法,可以消除这种电源干扰。CMOS运放电源抑制比。但在MOS大规模集成电路中,这种干扰往往是客观存在的,难以消除,因此,在MOS大规模集成电路中,设计高电源抑制比的运放显得十分必要。

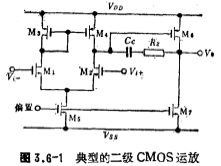

图3.6-1所示的电路是典型的二级CMOS运放,其正电源抑制比较差。CMOS运放电源抑制比。当正电源VDD上有一交变的信号电压Vs时,为保持输出驱动管M6电流不变(因M7管电流是恒定的),则在M6的栅极也同样有一信号电压Vs,也就是说,M6的漏极电压增量与M6的栅极增量相同,而M6的栅极与补偿电容Cc相连,因此,M6栅极的变化信号通过补偿电容Cc耦合到输出端,这样,交变信号电压Vs引起的变动信号可以在输出端得到。

由图3.6-1的等效电路分析可知(见参考文献[21]),其电源抑制比可表示为

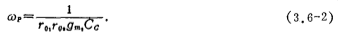

式中的 为运放的第一极点频率,

为运放的第一极点频率, (即GB)为运放的单位增益带宽。

(即GB)为运放的单位增益带宽。 可表示为

可表示为

式中 为输入级差分放大器的输出阻抗,

为输入级差分放大器的输出阻抗, 为输出级的输出阻抗,

为输出级的输出阻抗, 为输出级管M6的跨导,Cc为补偿电容。而

为输出级管M6的跨导,Cc为补偿电容。而 可以表示为

可以表示为

式中 为输入级差分放大器的跨导,Cc为补偿电容。

为输入级差分放大器的跨导,Cc为补偿电容。

由(3.6-1~3)式可知,电源的干扰频率较低时,图3.6-1电路的抑制比

,相当于60分贝。CMOS运放电源抑制比。随着电源的干扰频率增大,电源抑制比下降,即电源抑制比性能变坏。

,相当于60分贝。CMOS运放电源抑制比。随着电源的干扰频率增大,电源抑制比下降,即电源抑制比性能变坏。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助