电子技术论坛

信息来源: 时间:2021-1-19

CMOS运放的瞬间相响应与建立时间解析

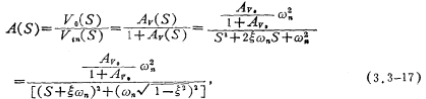

当t≥Ts时,运放进入线性放大状态,由图3.3-2得闭环的传递函数为

式中

由(3.3-17)式闭环放大器的极点为

显然,极点分布与阻尼系数ξ有关,因而建立时间 也与有关。

也与有关。

由(3.3-19)、(3.3-21)式,得到

当 1时,补偿电容Cc有如下关系,

1时,补偿电容Cc有如下关系,

利用(3.3-10)式初始条件及(3.3-17)式,可求得不同ξ值时的建立时间 (详细推导可参看文献[13])。

(详细推导可参看文献[13])。

1、ξ<1(有过冲情况)

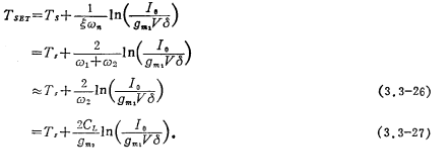

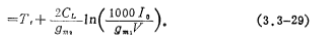

公式(3.3-27)第一项表示转换时间,第二项表示线性工作区的建立时间。若δ=0.001,则(3.3-26)、(3.3-27)式可写为

2、 =1(临界阻尼)

=1(临界阻尼)

上式的建立时间 可用图解法求得。

可用图解法求得。

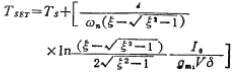

3、 〉1(过阻尼)

〉1(过阻尼)

由上面讨论可知,要缩短建立时间TSST,应提高运放的单位增益带宽(GB=Avoω1)和高频极点频率ω2,并且扩大输入级的动态范围(Io/gm1)。

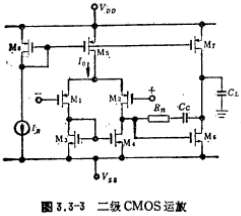

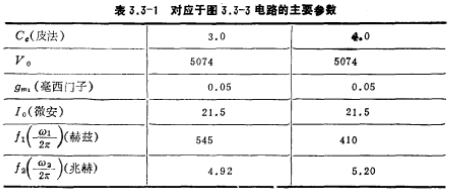

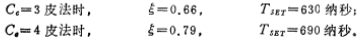

为获得较短的建立时间,取阻尼系数ξ小于1,通常取0.6~0.9。现对图3.3-3所示的CMOS运放电路进行瞬态分析。

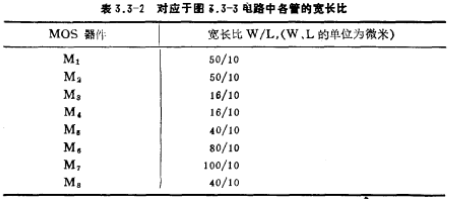

图中各主要参数见表3.3-1.各管的宽长比见表3.3-2.

将图3.3-3接成跟随器,输入电压为 伏阶跃信号,根据图3.3-3、表3.3-1的数据以及(3.3-23)、(3.3-27)式,可求得ξ=0.001时的建立时间TSST;

伏阶跃信号,根据图3.3-3、表3.3-1的数据以及(3.3-23)、(3.3-27)式,可求得ξ=0.001时的建立时间TSST;

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助