电子技术论坛

信息来源: 时间:2020-12-21

NMOS管的偏置电路分析及及解读过程

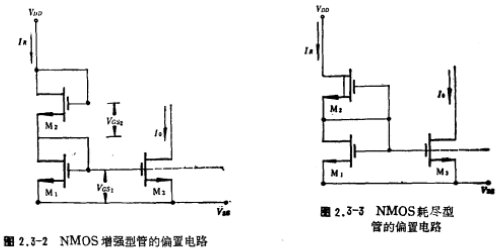

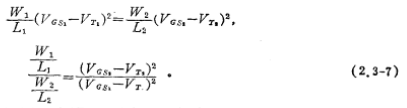

NMOS管的偏置电路有两种,一种是用增强型管作为等效电阻的偏置电路,另一种是用耗尽型管作为等效电阻的偏置电路,电路形式分别如图2.3-2,图2.3-3所示。

图2.3-2和图2.3-3中的M2管其作用相当于图2.3-1中的偏置电阻RB由MOS管的电流-电压特性可知,减小MOS管的沟道宽长比(W/L),即增大沟道长度L,可提高漏源两端的等效电阻阻值(这里说的等效电阻是指直流等效电阻,(VDS/ID))。如果M1、M2管的沟道宽长比决定后,参考电流IR也就确定了。反之,给定参考电流IR以及M1、M₂管的工作电压(VGS)可分别计算出M1管和M2管的沟道宽长比。先对图2.3-2电路进行讨论。

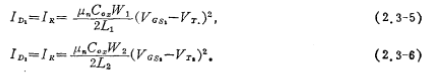

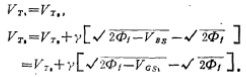

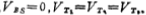

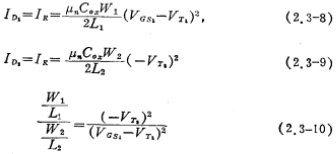

由图2.3-2可知,M1管和M2管的漏源电流ID相同,等于IR根据电流方程可得

由上述两个方程得到

上式的阈值电压VT1、VT2。分别表示为(见第一章(1.2-19)式)

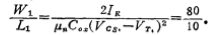

根据(2.3-5)、(2.3-7),可求得M1、M2管的沟道宽长比。现举例说明

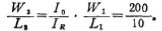

IR=80微安,VDD=2.5伏,VSS=-2.5伏,VT=1伏,μn=600厘米2/伏秒,tox=1000埃,Io=200微安。

为简单起见,假设M2管的衬底与源极连接, 试计算M1、M2和M3的沟道宽长比。

试计算M1、M2和M3的沟道宽长比。

由(2.3-5)式得

M2管的VGS为

由(2.3-7)式得

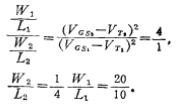

图中的电流源IO与IR的关系式为

M3管的沟道宽长比为

若取L1=L2=L3=10微米,

W1=80微米,W2=20微米,W3=200微米。

由(2.3-5~7)式及上例,可以看出,在给定IR的条件下,MOS管的VGS越大,其沟道宽长比越小。为了增大电流源IO输出的电压动态范围,通常 的电压值取得比较低。因此,当电源电压(VDD、VSS)较大时,势必增大M2管的

的电压值取得比较低。因此,当电源电压(VDD、VSS)较大时,势必增大M2管的 ,大大减小其沟道的宽长比。如果上例的电源电压改为VDD=7.5伏,Vss=-7.5伏,那么

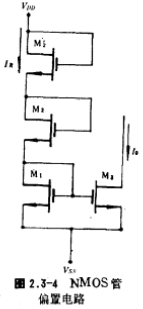

,大大减小其沟道的宽长比。如果上例的电源电压改为VDD=7.5伏,Vss=-7.5伏,那么 伏,W2/L2=W2/269L1,即M2管的沟道宽长比从W1/4L1减少到W1/269L1。为了不过多地减小M2管的沟道宽长比,可采用图2.3-4

伏,W2/L2=W2/269L1,即M2管的沟道宽长比从W1/4L1减少到W1/269L1。为了不过多地减小M2管的沟道宽长比,可采用图2.3-4

的电路形式。

对于图2.3-3的偏置电路,也可得如下表示式。

式中的 为耗尽型MOS管M2的夹断电压,其值为负值,图2.3-3图2.3-4NMOS管电路的设计方法与图2.3-2电路的设计方法相同。

为耗尽型MOS管M2的夹断电压,其值为负值,图2.3-3图2.3-4NMOS管电路的设计方法与图2.3-2电路的设计方法相同。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助