电子技术论坛

信息来源: 时间:2020-12-1

NMOS器件及工艺方法与流程详解

双层栅工艺上面介绍的工艺,都是用热生长二氧化硅膜作为栅介质材料。用二氧化硅作为绝缘介质,具有它的独特优点,它与硅有比较理想的界面接触,绝缘性和介电性也比较好,故仍然是当前平面工艺中较为理想的绝缘保护层。NMOS工艺。但随着对MOS电路要求的日益提高,就暴露出二氧化硅膜的不足之处。例如:

①二氧化硅膜内存在可动的钠离子,当温度升高时,会在一定的偏压下发生漂移,使器件性能不稳定;

②二氧化硅膜抗辐射能力差,使MOS器件受辐射而影响沟道状态和表面迁移率;

③二氧化硅中的正电荷会使硅表面感应负电荷,用二氧化硅作栅介质的N沟道MOS管容易耗尽,所以要做成增强型是十分困难的;

④二氧化硅本身多缺陷,并且与硅有相互作用。

为了克服以上缺点,提高电路性能,人们发现氮化硅(Si3N4)和三氧化二铝(Al2O3)薄膜的某些特性比二氧化硅更为优越,因此利用二氧化硅和氮化硅、三氧化铝的优点,组成了二氧化硅-氮化硅和二氧化硅-三氧化二铝的双层栅结构,制成了NMOS和MAOS器件,从而改善和提高了电路的性能。NMOS工艺。下面介绍两种薄膜的性质及其在MOS电路中的应用。

一、NMOS工艺

1、Si3N4的优点

NMOS工艺是采用SiO2-Si3N4双层结构作为MOS器件栅介质的工艺。这种工艺主要是基于氮化硅较二氧化硅优点更多,更为现想。

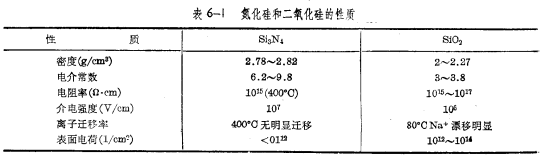

表6-1中分别列出了氮化硅和二氧化硅的性质。

从上表看出,采用Si3N4将有下列几点好处;

①Si3N4介电常数大,表面电荷密度低,对于制造低阈值电压增强型MOS器件是有利的,从而可与TTL电路相容,又因为有高的介电常数,可提高导电因子,有利于提高集成度。

②由于Si3N4的介电强度比SiO2大,有利于提高MOS绝缘栅的耐压。

③在Si3N4中,钠离子的迁移率是很低的,所以Si3N4可用来作为防止Na+侵入的掩膜;Si3N4的密度大,掩膜能力强,不但能掩蔽Na+,还可掩蔽多种杂质,而且化学稳定性好,有利提高器件的稳定性。

2、工艺流程

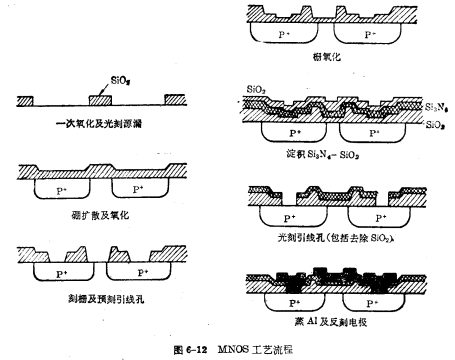

NMOS工艺,与常规MOS工艺相差不多,只是多了淀积Si3N4和腐蚀Si3N4两个工艺程序。下面以P沟道增强型器件为例,说明双层栅SiO2-Si3N4结构的工艺过程。

淀积Si3N4是在栅氧化以后进行的。NMOS工艺。Si3N4淀积以后,接着再淀积一层SiO2,作为腐蚀Si3N4的掩蔽膜。刻蚀时,先腐蚀掉引线孔上的SiO2,然后再用掺有25%硝酸的磷酸混合液,在140℃~160℃的条件下将Si3N4腐蚀掉,最后再将剩余的SiO2腐蚀掉。如图6-12所示。

如果采用1Ω·cm(100)面的P型Si衬底,绝缘层用SiO层(30nm)和Si3N4(180nm)

的双层介质,栅用金属A1,可以制成NMOS结构的N沟道增强型器件。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助