电子技术论坛

信息来源: 时间:2020-11-27

等平面硅栅N沟MOS工艺制作步骤及特点

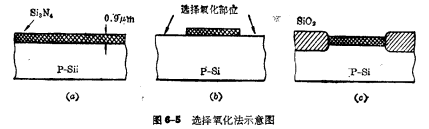

N沟道等平面工艺,又称”选择氧化法MOS技术”,它的特点是在硅衬底的某一部分有选择地进行氧化,而在不需要氧化的区域用 掩膜保护起来。它的基本方法由图6-5表示。首先在硅衬底上淀积一层薄的

掩膜保护起来。它的基本方法由图6-5表示。首先在硅衬底上淀积一层薄的 膜,厚度约为0.2~0.9μm,然后,刻去需要氧化部分的

膜,厚度约为0.2~0.9μm,然后,刻去需要氧化部分的 膜,接着用热氧化法进行氧化,生成一层约为1.0μm~1.1μm的氧化层。由于

膜,接着用热氧化法进行氧化,生成一层约为1.0μm~1.1μm的氧化层。由于 膜的热氧化速度极慢,并对氧气氛有掩载作用,所以

膜的热氧化速度极慢,并对氧气氛有掩载作用,所以 膜下面的部分并没有被氧化,而在氧化的区城内,随着氧化层厚度的增加,硅-二氧化硅的界面逐渐向衬底深处推移,所以约有一半的

膜下面的部分并没有被氧化,而在氧化的区城内,随着氧化层厚度的增加,硅-二氧化硅的界面逐渐向衬底深处推移,所以约有一半的 ,膜位于表面之上,另一半则陪于表面之下。这样,厚的

,膜位于表面之上,另一半则陪于表面之下。这样,厚的 层大部被埋在Si的表面内,使表面比较平整。器件就做在高出氧化层的合面上。

层大部被埋在Si的表面内,使表面比较平整。器件就做在高出氧化层的合面上。

推MOS常规工艺的讨论中知道,为了获得较高的场阈值电压,一次氧化往往需要做得很厚,最后在刻出引线孔时,造成很高的二氧化硅台阶,因此金属互联线要超过氧化物形成的陡销阶梯。硅栅N沟MOS工艺。在这些台阶的地方,金属层较薄,容易引起断线而发生开路,即使开始没有断裂,因金属薄的地方电流密度大,引起电迁移现象,在某些地方产生断线,而使器件早期失效。采用了上述等平面工艺,由于二氧化硅层是埋在衬底内的,消除了常规工艺中陡峭的二氧化硅台阶,大大提高了器件的可靠性。

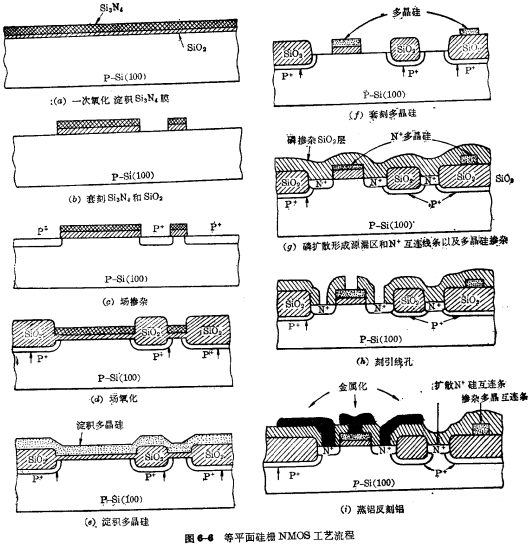

1、硅栅N沟MOS工艺制作步骤

(1)一次氧化及淀积 膜

膜

取电阻率为3~5Ωcm(100)晶面的P型硅单晶片,经过化学清洗后,进行一次氧化(做器件的绝缘栅),厚度为100~120nm;然后,用四氧化硅在氨气中进行分解反应,在硅片上淀积一层 薄膜,温度约为850℃。

薄膜,温度约为850℃。

(2)套刻氮化硅和二氧化硅

套刻后,只有在以后要形成源、漏、沟道区及扩散互连线的部分才留下二氧化硅和氮化硅层,其它部分都被刻去。

(3)场掺杂

首先在460℃的条件下,在硅片表面热分解淀积一层掺硼的二氧化硅层;接着,利用短时间的高温,将硼向硅表面扩散,使没有掩膜的部分(称为场区),掺进一定数量的硼。

(4)场氧化(厚氧化层生成)

首先将掺杂的氧化物腐蚀掉,接着在975℃的湿氧条件下,对无掩膜的硼掺杂区进行局部氧化,生长约1000~1100nm的厚氧化层。硅栅N沟MOS工艺。大约一半在硅原来的表面以下,另一半在表面以上。

(5)淀积多晶硅

先将氮化硅膜腐蚀掉,留下的二氧化硅薄膜作为器件的绝缘栅介质。将片子放在高温的氮气中退火后,就在硅片表面上淀积一层多晶硅膜,约为480~500nm。最后再进行热氧化处理。

(6)套刻多晶硅

刻出源、漏区的扩散窗口和外连线扩散条。

(7)磷扩散

在硅片表面上热分解淀积一层重磷掺杂的二氧化硅,然后,将硅片推入大约1050℃的恒温区内,在氮气中处理10~15分钟。这样,就进行了磷扩散,形成了扩散深度约为1Ωm的源漏和掺杂互连线的N+区,同时对多晶硅也进行了掺杂。

(8)光刻引线孔

提供源漏和栅的金属接触。

(9)蒸铝、反刻

有些工艺中,在蒸铝前先蒸发一薄层钛,然后再蒸铝,构成钛-铝双层金属。这对N沟道MOS集成电路特别有利,因为钛层能防止铝层因浅N+扩散结的位错和收缩面造成的失效。

反刻后,在480℃的氢气中进行30分钟的合金处理,以保证金属和硅接触良好,并消除硅-二氧化硅界面的表面态。硅栅N沟MOS工艺。最后,再用低温淀积法,使片子表面生长一层500nm厚的二氧化硅保护膜。

具体过程如图6-6(a)~(c)所示。

2、硅栅N沟MOS工艺工艺特点讨论

采用等平面工艺制造N沟道MOS电路,除了前面已经介绍的表面比较平整,没有陡前的氧化层台阶,金属引线不易发生断裂的优点以外,从整个制作过程看,还有另外一些较为突出的优点。

(1)在厚氧化区(场区)对硅表面进行局部掺杂。通过局都掺杂,提高了这些区域的表面浓度,使场阈值电压 大大提高。面在制作管子源、漏、沟道区的合面部分,仍然保持着原有的村底浓度,因此不会降低管子的沟道迁移率,从面提高了电路的速度。

大大提高。面在制作管子源、漏、沟道区的合面部分,仍然保持着原有的村底浓度,因此不会降低管子的沟道迁移率,从面提高了电路的速度。

(2)从图6-7 所示的结构可以看出,由于进行了场掺杂,场扩散区可起隔离的作用,使相邻器件N+区之间的寄生沟道漏电减小到最低限度。硅栅N沟MOS工艺。因此可以靠短器件之间的间距,从而大大提高了电路的集成度。

所示的结构可以看出,由于进行了场掺杂,场扩散区可起隔离的作用,使相邻器件N+区之间的寄生沟道漏电减小到最低限度。硅栅N沟MOS工艺。因此可以靠短器件之间的间距,从而大大提高了电路的集成度。

(3)因为制作器件的台面区的衬底浓度较低,估计管子的阈值电压VT约为0.2V~0.6V,显然是低了一点。为了提高阈值电压的数值,可以借助背面栅效应,在衬底加负偏压,使VT调节至1.4V~2.0V。加了负的衬底偏压以后,可使厚氧化区的场阔值电压提高到10V~20V,这就满足了电路工作的要求。

(4)在扩散的N+区和场掺杂的P+区之间构成的二极管,可以用来作为栅保护器件。

由于场掺杂P区表面的受主浓度很高,使这个二极管的雪崩击穿电压在20V~30V之间,而且是硬击穿。硅栅N沟MOS工艺。所以这种栅保护器件就不必象普通MOS电路的栅保护器件那样,在扩散结周围覆盖一个接地的栅电极。

(5)在上述工艺中,还使用了硅栅工艺,所以还具有硅栅工艺所具有的一切优点。

上述虽然较MOS常规工艺繁杂,但随着科学技术的发展,等平面硅栅NMOS工艺已成为制造大规模MOS集成电路的重要手段。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助