电子技术论坛

信息来源: 时间:2020-11-26

P沟道硅栅多品工艺流程及其版图设计

硅栅工艺”是采用掺杂的多晶硅来做MOS管栅电极的一种工艺,与上面介绍的常规铝栅工艺的不同点是先在硅片上生长一层薄的二氧化硅层(栅介质),接着淀积约为500nm的多晶硅薄层,然后刻出源、漏扩散区进行源漏扩散。P沟道硅栅工艺。“硅栅工艺”对于器件和集成电路的性能,较之常规的铝栅工艺,具有较多的特点。

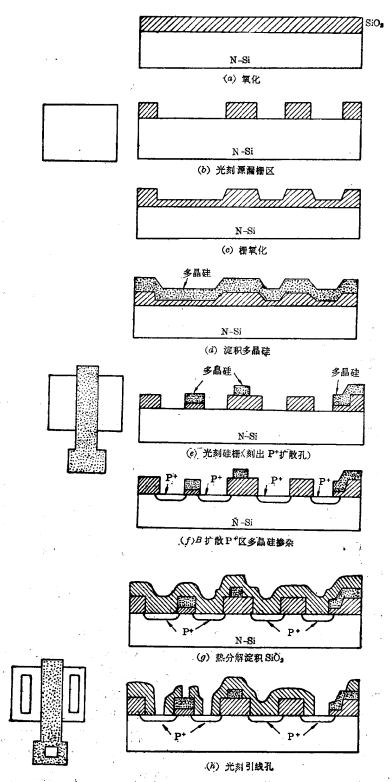

一、P沟道硅栅工艺流程

(1)一次氧化

抛光好的Si型出片(5~8Ω·cm)经清洁处理后,采用干-湿-干氧化程序,生长1μm的SiO2层。这样厚的氧化物,不仅作为扩散掩蔽,而且作为最终的场氧化物,对于减少寄生沟道是有利的。

(2)光刻源漏、栅区窗口(P区)

光刻后,经清洁处理,再进行栅氧化,生长100~120nm的薄SiO2层,构成MOS管的栅介质。

(3)沉淀多晶硅

淀积厚度为0.4~0.5μm。可用电子束蒸发淀积多晶硅,也可以采用硅烷热分解淀积多晶硅(即CVD技术)。

(4)反刻栅

确定多晶硅图形,包括硅栅及掺杂硅互连线。这次光刻无套准度问题。因为反刻栅既确定了栅区又确定了源漏区。

(5)硼扩散

刻好硅相图形的片子经清洁处理,即可进行翻扩做(扩散源漏区、P+互连区及硅栅重掺杂)。P沟道硅栅工艺。由于覆盖在上面的硅栅电极可以当作扩散掩膜,防止对沟道区掺杂,各个管子的源和漏区对于栅极可以自动对准。

扩散的结深<1μm,硅栅的R□在50~100Ω/口。

(6)低温淀积SiO2

去掉表硼硅玻璃层后,进行低温淀积SiO2 ,温度250~400℃,厚度300~500nm。之所以要用低温淀积,是为了避免再分布后薄层电阻下降。通常采用低温硅烷氧化法,也可采用正硅酸乙酯热分解方法。P沟道硅栅工艺。

为了起钝化作用,淀积SiO2 后,可进行确处理。

(7)光刻引线孔

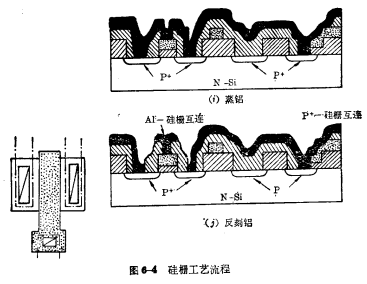

光刻引线孔,提供源漏和拥的金属接触,蒸铝后再反刻电极,确定Al互连图形。

其工艺流程由图6-4所示。

2、P沟道硅栅多品工艺

硅栅工艺最主要的是多晶工艺,即制备作为栅电极及互连线的多晶硅薄膜。通常采用蒸发或溅射方法,也可以用硅烷的热分解方法(即CVD方法)。

(1)多晶硅的淀积

如用电子束蒸发多晶硅,为了使蒸发的硅膜与SiO2 ,很好地粘附,衬底要保持在300℃。典型淀积速率是300nm/min。沉积多晶硅要求达0.4~0.6μm,电子束蒸发可提供清洁而均匀的硅膜。P沟道硅栅工艺。如果放硅片的架子采用行星转动式装置,则可克服台阶断裂的缺陷。电子束蒸发也存在一个间题,蒸发源上部熔化,而底部未熔化,这样受热不均匀,会引起硅滴飞溅到片子上,造成大颗粒。为克服这个缺点,应控制好蒸发温度及速率。

采用高频溅射也能获得均匀的硅层,但溅射没有电子束蒸发干净,会有重离子沾污。

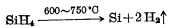

还有一种方法是采用硅烷在600~750℃时热分解淀积硅。这种方法获得的硅层的清洁度与均匀性介于蒸发和溅射之间。但多晶硅不象蒸发硅那样的无定型,而呈颗粒状,颗粒大小取决于生长条件。

化学反应式如下:

(2)多品硅腐蚀

多晶硅腐蚀也是硅栅工艺的重要步骤。硅栅工艺对硅栅尺寸必须严格控制,器件的宽长比很大程度上取决于硅栅尺寸的控制,所以对多晶硅的腐蚀条件是很讲究的。

腐蚀多晶硅通常用 腐蚀液。P沟道硅栅工艺。为了得到很好的控制,最好用较低被度的腐蚀液,溶液中HF和HNO2比例大小取决于要腐蚀多晶硅的厚度。

腐蚀液。P沟道硅栅工艺。为了得到很好的控制,最好用较低被度的腐蚀液,溶液中HF和HNO2比例大小取决于要腐蚀多晶硅的厚度。

多晶硅也可以采用Si的各向异性腐蚀剂。如乙二胺-H2O系(不含磷苯二酚),或乙二胺(180cm2)-磷苯二酚(30克)-纯水(80cm2),温度110℃。对掺硼多品晶硅腐蚀速率为 ,对没掺杂的多晶为1.4μm/min,对掺磷的多晶为2μm/min。

,对没掺杂的多晶为1.4μm/min,对掺磷的多晶为2μm/min。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助