电子技术论坛

信息来源: 时间:2020-11-10

MOS R-S管触发器工作原理及设计考虑详解分析

MOS触发器简介

触发器和其它逻辑部件,在第二章中,已介绍了“与”门、“或”门、“非”门、“与非”、“或非”及“与或非”等逻辑门。这些逻辑门的输出由输入状态决定,如果输入状态改变,输出也立刻作相应的改变。利用这些逐辑门可以实现逻辑计算和逻辑控制。但这些门电路不具备“记忆”信号的作用,输入信号一旦消失,输出信号就不复存在。在数字系统中,还需要具有计数、移位以及存贮指令和代码的电路,即要求这些电路具有“记忆”信号的功能。触发器就是具有“记忆”作用的电路,它具有两个稳定状态,可以把二进制代码的“1”和“0”存贮起来。因此,可以利用触发器来构成计数器、移位寄存器和存贮器等各种复杂的逻辑电路。R-S管触发器,本章主要介绍各种MOS型触发器和其它逻辑部件,诸如译码器、加法器、移位寄存器等的工作原理及其逻辑功能。

MOS R-S触发器

触发器种类很多,如按功能可以分为R-S触发器、J-K尽触发器、D触发器等类型,按工作原理可以分为静态触发器、准静态触发器和动态触发器,但它们的逻辑结构是基本相同的。下面将分别介绍各种触发器的电路结构及其逻辑功能。

一、R-S触发器

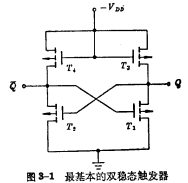

1、两级倒和器组成的双稳态触发器

图3-1是由两级PMOS倒相器交叉耦合的双稳态触发器电路。在PMOS电路中,有正逻辑规定,也有负逻辑规定。这里我们采用负逻辑规定来讨论PMOS电路的工作原理。

在这个PMOS电路里,

组成第一级倒相器,

组成第一级倒相器,

组成第二级倒相器。第一级倒相器的输出端接第二级倒相器的输入端,第二级倒相器的输出端接第一级倒相器的输入端,两个输出端分别用Q和Q表示。

组成第二级倒相器。第一级倒相器的输出端接第二级倒相器的输入端,第二级倒相器的输出端接第一级倒相器的输入端,两个输出端分别用Q和Q表示。

这种触发器具有两个稳定状态。一个稳定状态是

导通而

导通而 截止,另一个稳定状态是

截止,另一个稳定状态是 导通而

导通而 截止。如果没有外界的影响,电路将长期处于某一个稳定状态,所以通常称它为双稳状触发器。

截止。如果没有外界的影响,电路将长期处于某一个稳定状态,所以通常称它为双稳状触发器。为了说明触发器的这种特点,我们先假定

导通,此时输出端Q为“0”电平。由于输出端Q与另一个倒相器的输入端相连,因此可以使

导通,此时输出端Q为“0”电平。由于输出端Q与另一个倒相器的输入端相连,因此可以使 截止,使输出端

截止,使输出端 为“1”电平,输出端

为“1”电平,输出端 与

与 的栅极又是连在一起的,这样就保证了

的栅极又是连在一起的,这样就保证了 导通。如果没有外来信号,这种状态就会长期保持下去。这是触发器的第一个稳定状态。

导通。如果没有外来信号,这种状态就会长期保持下去。这是触发器的第一个稳定状态。“当好

导通时,输出端Q为“0”电平,同样道理会使

导通时,输出端Q为“0”电平,同样道理会使 截止,使输出端Q为“1”电平,这个“1”电平又加在

截止,使输出端Q为“1”电平,这个“1”电平又加在 的栅极上,保证了

的栅极上,保证了 的导通。这是触发器的另一个稳定状态。

的导通。这是触发器的另一个稳定状态。通常把

称为“0”状态,而

称为“0”状态,而 就称为“1”状态。由此可见,触发器能够把电信号“1”或“0”长期保存下来,起到“记忆”电信号的作用。

就称为“1”状态。由此可见,触发器能够把电信号“1”或“0”长期保存下来,起到“记忆”电信号的作用。如果要使触发器从一个稳定状态变到另一个稳定状态,就需要给触发器施加一个信号。假设触发器原来处于“0”状态,即

,如果把端接地,就会使

,如果把端接地,就会使 截止,使Q由“0”变到“1”,从而导致

截止,使Q由“0”变到“1”,从而导致 导通,使Q由“1”变到“0”,触发器就从“0”状态变到“1”状态。这种状态转变,通常叫做触发器的“翻转”。

导通,使Q由“1”变到“0”,触发器就从“0”状态变到“1”状态。这种状态转变,通常叫做触发器的“翻转”。上述触发器,Q和Q既是输入端又是输出端,因此在实际电路中是不能应用的。能够应用的触发器,其输入端和输出端必须是分开的。下面介绍由上述最简单触发器演变出来的各种触发器电路。

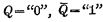

2、基本的R-S触发器

R-S触发器又叫做置位-复位触发器。其电路如图3-2所示。这是在上述双稳态触发器的基础上,加上 两管,使

两管,使 分别与

分别与 相并联。其实,它是由两个交又相连的“或非”门电路构成的。Q和

相并联。其实,它是由两个交又相连的“或非”门电路构成的。Q和 同样表示两个输出端,R和S是两个输入端。

同样表示两个输出端,R和S是两个输入端。(1)工作原理

假设触发器开始处于“0”状态(

),即

),即 导通

导通 截止。为了使触发器由“0”状态变到“1”状态,只要使输入端R保持“0”电平,而在S端加一个“1”“电平,因为

截止。为了使触发器由“0”状态变到“1”状态,只要使输入端R保持“0”电平,而在S端加一个“1”“电平,因为 电平时,

电平时, 导通,使

导通,使 输出“0”电平,而使

输出“0”电平,而使 截止,

截止, 截止后使Q变成“1”电平,反过来使

截止后使Q变成“1”电平,反过来使 导通。这样,即使S输入端上的信号“1”没有了,触发器还会保持

导通。这样,即使S输入端上的信号“1”没有了,触发器还会保持 裁止、

裁止、 导通的“1”状态。因此输入端S叫做置“1”输入端,又做置位输入端。

导通的“1”状态。因此输入端S叫做置“1”输入端,又做置位输入端。要使触发器由“1”状态恢复到“0”状态,只要使S端保持“0”电平,而在B端上加一个“1”电平就行了。因为

时,

时, 立刻导通,使Q由“1”变到“0”,这个“0”又输入到

立刻导通,使Q由“1”变到“0”,这个“0”又输入到 管的栅极

管的栅极 使截止,由于原来

使截止,由于原来 是截止的,所以由“0”变到“1”。触发器由“1”状态恢复到“0”状态。因此R端叫做置“0”输出端,又称复位输入端。

是截止的,所以由“0”变到“1”。触发器由“1”状态恢复到“0”状态。因此R端叫做置“0”输出端,又称复位输入端。在R-S触发器里,如果R和S两个输入端都保持“0”电平,则

都截止,触发器保持原来的状态不变。如果R和S两个输入端都加上“1”电平,则

都截止,触发器保持原来的状态不变。如果R和S两个输入端都加上“1”电平,则 都导通,两个输出端Q和

都导通,两个输出端Q和 都变成了“0”电平,使

都变成了“0”电平,使 都截止,破坏了触发器的正常状态。当R和S两个输入端都由1”电平恢复到“0”电平后,触发器的状态就不能确定,不能肯定是处于“1”状态,还是处于“0”状态。因此,在R-S触发器的工作过程里,B和S两个输入端上不能同时加“1”电平。下面是R-触发器的逻辑图及真值表。

都截止,破坏了触发器的正常状态。当R和S两个输入端都由1”电平恢复到“0”电平后,触发器的状态就不能确定,不能肯定是处于“1”状态,还是处于“0”状态。因此,在R-S触发器的工作过程里,B和S两个输入端上不能同时加“1”电平。下面是R-触发器的逻辑图及真值表。

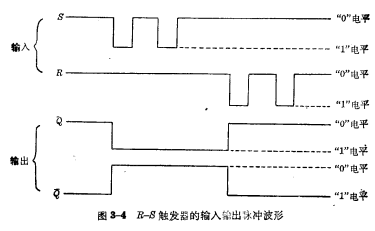

为了更好地描述R-S触发器的工作过程,我们在图3-4中画出了它的输入和输出脉冲被形。从图中可以看出,在S端加“1”电平,就可以使触发器由“0”状态变为“1”状态,但如果触发器已经处于“1”状态,在端上加负脉冲就不会使触发器再发生变化。若在R端加“1”电平,可以使触发器由“1”状态变为“0”状态,如果触发器已经处于“0”状态,在R输入端加“1”电平,也不会使触发器再发生变化。从图3-4看到,Q和

的变化是同时发生的,这是理想的情况。在实际上,由于延迟效应,

的变化是同时发生的,这是理想的情况。在实际上,由于延迟效应, 的变化比R、S的变化要滞后一些。

的变化比R、S的变化要滞后一些。

(2)设计考虑

要使电路具有上述的两个稳定状态,必须正确地选择电路中各个器件的参数和工作条件。否则,电路就不能保证有两个稳定的工作状态,不能实现触发器的逻辑功能。下面介绍电路正常工作所需要的条件及设计思想。①最高工作频率

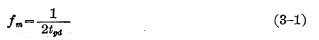

为了使R-S触发器稳定地工作,触发脉冲的宽度必须大于 ,因此触发器的最高频率为:

,因此触发器的最高频率为:

其中

为一级门的平均传输延迟时间。(3-1)式给出了最高工作频率与组成触发器各个逻辑门延迟时间的关系。因此,在设计时,就可以根据工作频率的要求,确定出各逻辑门的延迟时间,从而确定各逻辑门的器件参数。

为一级门的平均传输延迟时间。(3-1)式给出了最高工作频率与组成触发器各个逻辑门延迟时间的关系。因此,在设计时,就可以根据工作频率的要求,确定出各逻辑门的延迟时间,从而确定各逻辑门的器件参数。②输出电平

要使R-S触发器能保持正常工作,输出端Q(或

)的“0”电平的绝对值必须小于门电路的关门电平,而“1”电平的绝对值必须大于门电路的开门电平,使门电路可靠地截止和充分导通,从而保证触发器处于稳定的工作状态。根据这个要求,可以确定门电路负载管和输入管的跨导比。

)的“0”电平的绝对值必须小于门电路的关门电平,而“1”电平的绝对值必须大于门电路的开门电平,使门电路可靠地截止和充分导通,从而保证触发器处于稳定的工作状态。根据这个要求,可以确定门电路负载管和输入管的跨导比。③静态功耗

R-S触发器是双稳态电路,组成触发器的两个门,在工作时总有一个门导通,另一个门截止。因此计算触发器的静态功耗只考虑一个门即可。与倒相器的设计一样,功耗和速度是矛盾的,它们与负载管的几何尺寸有关。(3)基本R-S触发器的特点

从上面分析知道,它是由两个“或非”门连结而成,电路对称,结构简单,是其它触发器的基础。它的特点是:①具有两个稳定的工作状态,有“记忆”信息的功能。

②通过R、S输入端分别加负脉冲,可以实现置“0”或置“1”的功能。但是,R-S触发器状态的存入无法从时间上得到控制,而在各单元之间必须协同动作的中大规模集成电路中,难以直接应用。况且R-S触发器只有置“1”置“0”的功能,R、S端不能同时为“1”脉冲。所以必须对基本的R-S触发器进行不断的改进,使其具有完善的功能。

3、R-S-T燃发器

在计算机使用触发器时,常常要用脉冲来控制触发器翻转的时间,这种控制触发器翻转时间的脉冲叫做时钟脉冲,常用符号

来表示。只有当时钟脉冲输入时,触发器才会根据输入端上的电平来决定它的状态;而没有时钟脉冲输入时,不管输入端上的状态如何变化,触发器都不会改变原来的状态。

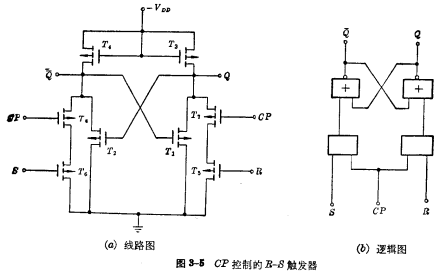

来表示。只有当时钟脉冲输入时,触发器才会根据输入端上的电平来决定它的状态;而没有时钟脉冲输入时,不管输入端上的状态如何变化,触发器都不会改变原来的状态。图3-5所示的R-S-T 触发器(或称同步触发器),就是受时钟脉冲

控制的R-S触发器,它与R-S触发器的电路相比,多了

控制的R-S触发器,它与R-S触发器的电路相比,多了 两个MOS管,它们的栅极都要受到时钟脉冲控制。如果

两个MOS管,它们的栅极都要受到时钟脉冲控制。如果 为

为 不能导通,R、S不能起作用,触发器不会改变原来的状态。只有当

不能导通,R、S不能起作用,触发器不会改变原来的状态。只有当 为“1”电平时,

为“1”电平时, 才导通,此时R-S就和前述的触发器一样,完成触发器的逻辑功能。

才导通,此时R-S就和前述的触发器一样,完成触发器的逻辑功能。

4、主从R-S触发器

上面所讲的R-S触发器结构虽然简单,但它的性能还不完善,不能进行计数,也不能构成移位寄存器。为了使触发器的性能更趋完善,就需要作进一步改进。为此,发展了一种主从结构形式的R-S触发器,它能使外来信息在时钟脉冲 作用的时间内送入主触发器进行暂存,然后在相反时钟脉冲(称为补时钟脉冲

作用的时间内送入主触发器进行暂存,然后在相反时钟脉冲(称为补时钟脉冲 )的时间内,将主触发器存贮的信息转移给从触发器。

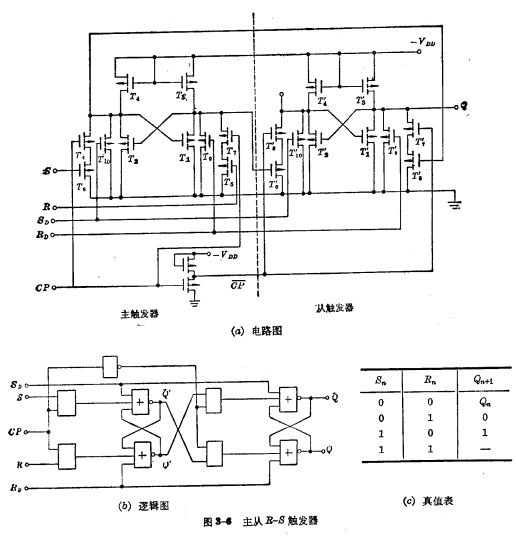

)的时间内,将主触发器存贮的信息转移给从触发器。图3-6是由两个独立的R-S-T触发器组成的主从触发器,左边的是主触发器,右边的是从触发器。其联结方法是将主触发器的Q'及

端分别与从触发器的S'、R'端联接。其中

端分别与从触发器的S'、R'端联接。其中 和

和 分别为主从触发器的预置位管,

分别为主从触发器的预置位管, 为预置位输入端。当

为预置位输入端。当

时,主从触发器处于“0”状态。

时,主从触发器处于“0”状态。 和

和 是分别受

是分别受 和

和 脉冲控制的器件。由于

脉冲控制的器件。由于 和

和 的控制,就使主、从两触发器隔离开来,消除了触发器在一个时钟脉冲作用期间,可能出现多次翻转的空翻现象。

的控制,就使主、从两触发器隔离开来,消除了触发器在一个时钟脉冲作用期间,可能出现多次翻转的空翻现象。下面来分析主从R-S触发器的功能。当时钟脉冲CP由“0”变到“1”时,主触发器的状态变化与上面讲的单个R-S触发器相同。此时由于

由“1”变到“0”,

由“1”变到“0”, 由导通变截止,所以从触发器的状态不变。当

由导通变截止,所以从触发器的状态不变。当 由“1”变到“0”时,

由“1”变到“0”时, 管截止,这时主触发器威将原来的信号贮存下来,同时由于

管截止,这时主触发器威将原来的信号贮存下来,同时由于 从“0”变到“1”,

从“0”变到“1”, 导通,主触发器的状态就可转移给从触发器。

导通,主触发器的状态就可转移给从触发器。

在设计电路时,一般主触发器各器件的W/L都要比对应的从触发器各器件的W/工小些,因为主触发器只要驱动从触发器,负载不大。然面从触发器的输出一般要接较大的负载,所以从触发器各器件的W/L就要增大。当输出端接的负载很大时,就有必要在输出端再增加一级驱动器,否则从触发器的晶片占有面积会太大。联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助