电子技术论坛

信息来源: 时间:2020-11-9

CMOS门电路(与非门、或非、非门、传输门等)详细介绍

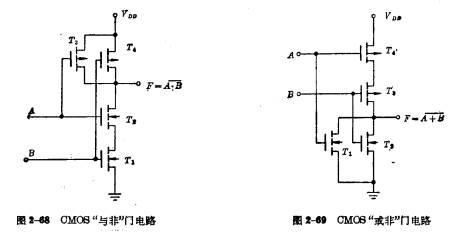

1、CMOS“与非”门和“或非”门电路

图2-68为CMOS“与非”门电路,其中 为两个串联的NMOS管,

为两个串联的NMOS管, 为两个并联的PMOS管,

为两个并联的PMOS管, 与

与 的栅极连接在一起作为输入端

的栅极连接在一起作为输入端 ,

, 与

与 的栅极连接作为输入端

的栅极连接作为输入端 ,

, 的漏与

的漏与 的漏连结,引出输出端F。当A与B同时输入为“1”(VDD)时,

的漏连结,引出输出端F。当A与B同时输入为“1”(VDD)时, 导通,

导通, 截止,输出为“0”电平;当A、B之间任一输入为“0”电平,两个串联的N管

截止,输出为“0”电平;当A、B之间任一输入为“0”电平,两个串联的N管 对地没有通路,而两个并联的P管,总有一个导通,等效导通电阻很小,电源电压几乎全部降落在

对地没有通路,而两个并联的P管,总有一个导通,等效导通电阻很小,电源电压几乎全部降落在 管上,所以输出为“1”电平;当A、B全为“0”电平时,截止

管上,所以输出为“1”电平;当A、B全为“0”电平时,截止 导通,输出仍为高电平“1”。所以电路具有“与非”的逻辑功能。

导通,输出仍为高电平“1”。所以电路具有“与非”的逻辑功能。

图2-69为“或非”门,其连接方法正好和“与非”门相反,两个N管 是并联的,两个P管

是并联的,两个P管 是串联的。输入端A或B只要有一个输入“1”电平,NMOS就有一个导通,输出就为“0”电平,只有A、B均为“0”时,使

是串联的。输入端A或B只要有一个输入“1”电平,NMOS就有一个导通,输出就为“0”电平,只有A、B均为“0”时,使 均截止,才会输出“1”电平。所以电路具有“或非”的逻辑功能。

均截止,才会输出“1”电平。所以电路具有“或非”的逻辑功能。

如果在“与非”门、“或非”门后面加一级倒相器,就构成CMOS“与”门和CMOS“或”门电路。

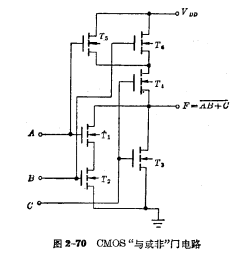

2、CMOS“与或非”门

图2-70为CMOS“与或非”门电路,是由三个NMOS管组成输入管,三个PMOS管组成负载管。输入管的联结方法与单沟道“与或非”门的相同。三个负载管的联结方法是 并联,然后与

并联,然后与 串联。栅极的联结方法是串联的输入管

串联。栅极的联结方法是串联的输入管 分别与并联的负载管

分别与并联的负载管 联结在一起,构成A、B输入端,并联的输入管

联结在一起,构成A、B输入端,并联的输入管 与串联的负载管

与串联的负载管 联结在一起,构成

联结在一起,构成 输入端。

输入端。

从上面讨论可知,当CMOS门电路为多输入端时,各输入管支路是串联形式,其对应的负载管支路是并联形式。相反,各输入管支路是并联形式,则负载管是串联形式。

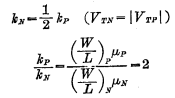

3、CMOS事联、并联门器件几何尺寸的考虑

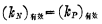

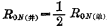

在CMOS倒相器噪声容限的讨论中知道,要获得最大的直流噪容,必须满足 的条件。对于多输入端的“或非”、“与非”门(或称并联、串联门),其

的条件。对于多输入端的“或非”、“与非”门(或称并联、串联门),其 因子分别要用

因子分别要用 有效和

有效和 有数来表示;要获得最大的噪容,必须满足

有数来表示;要获得最大的噪容,必须满足 然的条件。

然的条件。

下面分别讨论“或非”门和“与非”门器件尺寸的确定原则:

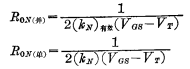

(1)“或非”们电路的器件尺寸当输入管是并联门时,如图2-69所示。若两个N管全导通时,并联两管的导通电阻是单个管子的1/2,即 ,由于

,由于

所以,可得到 。但通常只要两并联管中任一管导通,门电路就可输出“0”

。但通常只要两并联管中任一管导通,门电路就可输出“0”

电平。因此有

输入管并联时,负载管是串联的。若两个串联的P管同时导通,其导通电阻为单一管子的2倍,即 ,因此可得

,因此可得

根据获得最大噪容要求的条件,可得

若为 个输入端,则有:

个输入端,则有:

若取 ,则:

,则:

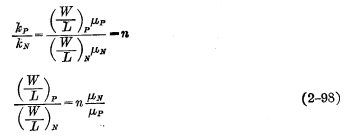

(2-100)式表明,在 个输入端的“或非”门电路中,串联器件(负载管)的沟道宽度近似为并联器件(输入管)的

个输入端的“或非”门电路中,串联器件(负载管)的沟道宽度近似为并联器件(输入管)的 倍(认为

倍(认为 )。

)。

(2)“与非”门电路器件尺寸与上面的方法类似,可以根据 的条件,得到;

的条件,得到;

(2-101)式表明,在 个输入端的“与非”电路中,串联器件(输入管)的沟道宽度,约为并联器件(负载管)的%倍(认为

个输入端的“与非”电路中,串联器件(输入管)的沟道宽度,约为并联器件(负载管)的%倍(认为 )。

)。

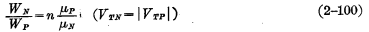

4、CMOS缓冲输出

大多数CMOS器件由于具有比较高的输出阻抗,限制了供给或吸收电流的能力,因此用来驱动CMOS电路是完全合适的。可是,当需要驱动TTL电路时,就需要提供较大的驱动电流或吸收电流(图2-71)。因此,必须设计具有低阻抗输出的专用电路。这种电路的形式与典型的CMOS倒相器相同,不过器件的尺寸要比标准的CMOS晶体管大得多。器件的尺寸可以根据驱动电流或吸收电流的大小,从电流方程来决定。

5、CMOS三态输出电路

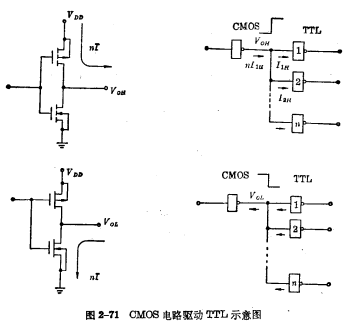

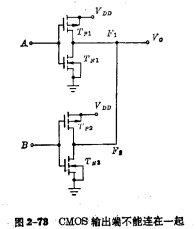

在许多数据传输中,经常需要将来自各个不同点的信号供给一根公共输出线,如图2-72所示。那么能否按图2-73将各个CMOS电路的输出端直接连结在一起呢?显然是不可以的。

从图2-73可以看到,如果倒相器A的输出端 是“1”电平,倒相器B的输出端

是“1”电平,倒相器B的输出端 是“0”电平,这时

是“0”电平,这时 和

和 导通,从电源VDD至地有一条通路。由于

导通,从电源VDD至地有一条通路。由于 和

和 的导电阻较高,且二者几乎相等,所以输出V。将是

的导电阻较高,且二者几乎相等,所以输出V。将是 ,既不是高电平又不是低电平。因此输出状态不能确定。

,既不是高电平又不是低电平。因此输出状态不能确定。

为了能在公共总线上实现如图2-72所示的连接,需要CMOS电路有三态输出的功能。所谓三态输出,就是电路的输出状态不仅有高电平与低电平输出,而且还有一个第三态(或称高阻态)。电路处于第三态时,负载管与输入管均处于截止态,其逻辑电平由与它并联在公共总线上的其它逻辑门的输出状态决定。电路处于第三态时,其输出端被全部截止的高阻器件所隔离,故本身既无确定的状态,也不会影响其它电路。

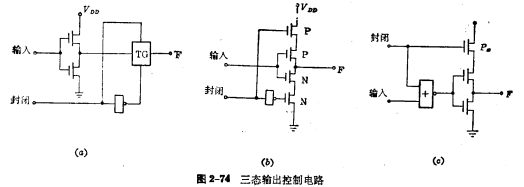

CMOS电路可以方便地实现三态输出功能,图2-74所示为实现三态输出的几种方法。

在图2-74(a)中,一个传输门与输出端串联。当传输门截止时,F和输出电路断开,当传输门导通时,F点的状态跟着倒相器输入端变化。

在图2-74(b)中,当禁止信号是高电平时,与倒相器串联的附加P管和N管都截止,有效地切断了电源VDD,使倒相器处于第三态;当封闭信号为低电平时,两个附加的P管和N管都导通,F 点的状态跟着倒相器变化。

在图2-74(c)中,封闭信号为高电平时, 截止,输入端不管是何信号,倒相器栅极的“或非”门输出都是低电平,

截止,输入端不管是何信号,倒相器栅极的“或非”门输出都是低电平, 截止,倒相器处于第三态。当封闭信号为低电平时,

截止,倒相器处于第三态。当封闭信号为低电平时, 导通,F 就跟着倒相器变化。

导通,F 就跟着倒相器变化。

三态输出电路不仅在简单的门电路中使用,而且在较复杂的电路中也经常使用。

当三态器件的输出被封闭时,它有一个类似于典型CMOS输入电容的寄生电容。其值约为10~15pF。因此,在图2-72中的任何器件的驱动,总线必须对所有与它连接的全部输入和输出电容以及全部衔接线的电容充电,从而使电路降低了工作速度,除了由电容引起的延迟以外,还必须考虑禁止电路需要的导通和截止时间。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助