电子技术论坛

信息来源: 时间:2020-10-26

MOS管主要参数及重要参数详细说明

一、MOS管直流参数

1、漏源截止电流Ioff

对于增强型MOS管,在VGS=0时,管子截止,漏源之间不能导通,即漏源电流应该为零。但由于PN结反向漏电等原因,所以漏源之间仍有很小的漏电流通过,常称为截止漏电流,用Ioff表示。实际上引起的漏电不仅有PN结反向漏电,还有沟道漏电。

2、饱和漏极电流IDSS

对于耗尽型MOS管,在VGS=0时,沟道已经存在,MOS管的漏、源两扩散区已经通导。当VGS一定且足够大时,漏极电流的饱和值叫做MOS管的饱和漏极电流,用IDSS表示。MOS管主要参数。根据MOS管的饱和电流公式,用VGS=0代入,可得到耗尽型MOS管的饱和漏极电流为:

该值对于N沟道耗尽型MOS管取正值,对P沟道耗尽型MOS管取负值。

3、栅源直流输入阻抗

MOS管的栅和源是用栅介质SiO2绝缘层隔离开来的,在组成电路时,栅和源通常作为输入端。所谓栅源直流输入阻抗 就是SiO2层的绝缘电阻。MOS管主要参数。栅氧化层愈厚,质量愈好,绝缘电阻就愈高。如果结构完整的热生长的SiO2,厚度在150nm左右时,绝缘电阻可达1012Ω以上,如果在栅极与沟道之间加一定的电压,能通过栅氧化层的电流是极微小的,一般小于10-14A。这是MOS管的可贵特性之一。

就是SiO2层的绝缘电阻。MOS管主要参数。栅氧化层愈厚,质量愈好,绝缘电阻就愈高。如果结构完整的热生长的SiO2,厚度在150nm左右时,绝缘电阻可达1012Ω以上,如果在栅极与沟道之间加一定的电压,能通过栅氧化层的电流是极微小的,一般小于10-14A。这是MOS管的可贵特性之一。

4、导通电阻

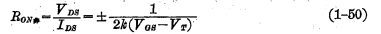

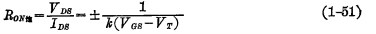

当MOS管工作在非饱和区,VDS很小时,特性曲线是直线,即IDS与VDS成正比,这时管子相当于一个纯电阻,即当VDS很小时,(1-46)式可略去 这一项,非饱和区的电流公式可写成:

这一项,非饱和区的电流公式可写成:

在这种情况下,漏源电压与漏源电流IDS的比值就叫导通电阻,常用RON表示。

可见,导通电阻与(VGS-VT)成反比,当VGS≈VT时,RoN变得很大,即反型层几乎消失。另外,RoN与沟道长度L成正比,与沟道宽度W成反比。

可以想到,如果VDS-VGS-VT,MOS管的工作进入饱和,这时的沟道电阻应为:

可见,临界饱和时的沟道导通电阻是非饱和区导通电阻的2倍。

5、漏源击穿电压BVDS

在前面讨论MOS管的输出特性曲线时曾提到,当漏源电压VDS超过一定限度时,就会产生击穿,使漏电流急剧增加。漏源击穿电压是有两个因素决定:

(1)漏扩散区与衬底之间的PN结击穿

当MOS管的源与衬底相连时,在漏源间施加电压就等于在漏极与衬底之间的PN结上施加一个反向电压。当VDS很大时,PN结的耗尽区变得很宽,势垒区中电场变得很大,VDS大到某一数值后,势垒区中就会产生雷崩击穿,耗尽层这完全与双极型管的PN结击穿一样。MOS管主要参数。但必须指出,对于MOS器件,由于源漏扩散区一般为浅结扩散,在图1-26漏扩散区附近的耗尽区电场分布示意图浅PN结的边缘处,有较大的弯曲,在弯曲处会产生较强的楼角电场,所以PN结击穿首先在这里发生,致使BVDS大大降低。另外,对MOS管的扩散区来说,金属栅电极盖住了扩散区的边缘部分,如图1-28所示。由于栅电场的影响,击穿电压的大小也会受到较大的影响。例如,假定VDS=20V,VGS=5V,则栅极相对漏极是负电位,所以会使栅与漏的覆盖部分电场加强,使击穿电压降低。

(2)漏源之间的穿通现象

对于一个增强型器件,一般情况下,当Vs=0,VGs=0时,硅表面没有沟道存在,源漏之间是不导通的。当漏源间加上电压后,只会有极微小的PN结反向漏电流。但当VDS不断加大,漏区附近的耗尽层亦相应地不断展宽。当VDS大到某一程度,漏区周围的耗尽层扩展到与源扩散区相交迭时,源扩散区里的大量电子,就会在强电场的作用下,直接从源扩散区通过耗尽区扫入漏区,产生了很大的电流,这就是漏源穿通效应。如图1-29所示。

特别是对于衬底电阻率p比较高和沟道长度L比较小的MOS管,比较容易形成穿通现象。

穿通电压也象击穿电压一样,使最大漏源工作电压VDS受到限制,对于一个具体的管子,到底是先发生PN结击穿,还是先发生穿通现象,要看具体结构而定。如果衬底电阻率较低,沟道又较长的管子,一般总是由雪崩击穿电压来决定BVDS的大小。MOS管主要参数。而对于衬底电阻率较高,沟道长度L较短的管子,很前能在发生雪崩击穿以前就发生了穿通现象。

对于在高电阻率的衬底材料上进行的浅结扩散,耗尽层的宽度可用突变结近似计算,其耗尽层厚度为:

其中V在这里就是VDS,VD为PN结自建电势。当 时,就发生了穿通效应,如果略去了VD,则由穿通现象引起的漏源击穿电压为:

时,就发生了穿通效应,如果略去了VD,则由穿通现象引起的漏源击穿电压为:

对于用掺杂浓度为5×1014个/cm2(相当于p-10 .cm)的P型衬底,做成沟道长度

.cm)的P型衬底,做成沟道长度 的MOS管,根据(1-53)式计算,

的MOS管,根据(1-53)式计算, 约为35~40V,比一般的PN结击穿电压低得多,因此,实际测量所得到的漏源击穿电压是由穿通现象引起的。

约为35~40V,比一般的PN结击穿电压低得多,因此,实际测量所得到的漏源击穿电压是由穿通现象引起的。

6、栅击穿与栅保护

(1)栅击穿

在MOS管中,栅极与沟道之间隔着一层氧化膜,这种结构与电容器的结构一样,当栅源电压或栅漏电压超过一定限度时,就会引起氧化膜的击穿,使栅极与氧化膜下面的硅发生短路现象。氧化膜一旦被击穿,MOS管就损坏了,所以在使用MOS管时,在栅极上不能加过高的电压。

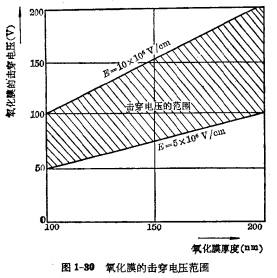

从实验知道,氧化膜的击穿电压和氧化膜的厚度成正比,其击穿的电场强度E值在5×106~10×106V/cm之间。通常情况下,栅极下面的氧化膜厚度约在100~200nm之间,它的击穿电压如图1-30所示范围,由于氧化膜150nm的质量好坏不同,对于同样的厚度,击穿电压也有所不同。MOS管主要参数。对于厚度为150nm的氧化膜来说,它的击穿电压在75~120V之间,实际上,由于SiO2中存在着缺陷、针孔以及外来沾污,致使最大耐压有所降低。

由于MOS器件的栅电容量很小,并且栅绝缘电阻很大,因此很小的电量就会造成很高的电压使栅击穿。若栅电容为2pF,那么仅1.5×10-10C的电量,就可造成栅与衬底间达75V的高电压,使栅氧化层击穿。栅击穿后,栅电流急速增加。有人研究得到,在击穿点的电流密度可达 光谱观察到的峰值温度接近4000K。

光谱观察到的峰值温度接近4000K。

(2)栅保护

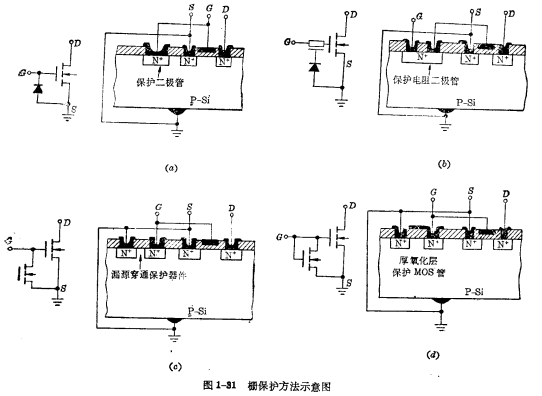

预防栅击穿是一个非常被人们重视的问题。防止栅击穿的方法很多,例如所有的仪器、电源、烙铁都要良好的接地,器件不用时要用导电材料包住等。不过这些方法都不能使栅极得到完全的保护,因此人们想出了利用栅保护器件,使器件的栅极不致轻易被击穿。对于MOS电路,除了在使用、保存中要注意静电击穿外,还要在电路内部,制造保护器件。其方法是很多的,但基本原理是类似的。一般在外引线与栅之间有一个接触电阻和一个并联的保护元件。这个元件在正常工作电压范围内,电阻很大,所以不影响电路的正常工作,但当栅极电压超过一定范围(例如接近栅击穿电压)时,它的电阻变得很小,就在输入端形成一个低阻通路,将感应的静电荷泄放掉,使栅极得到保护。图1-31是目前常用的几种输入栅保护方法。

其中,图1-31(a)为二极管保护,预先设计二极管的反向击穿电压低于MOS管的栅击穿电压BVGS。当输入电压由于某种原因大于二极管的反向击穿电压时,它就提供了泄放静电回路,使MOS管的栅得到保护。图1-31(b)是在输入栅中串一个扩散电阻,然后,再并联一个反向二极管。图1-31(c)为漏源穿通保护器件,其穿通击穿电压低于栅击穿电压。图1-31(d)为场致反型保护器件,它的栅介质为厚氧化层,约为MOS管的十倍。MOS管主要参数。以前讲到,MOS品体管的阔电压与氧化层的厚度成正比,氧化层愈厚,VT就愈大。所以当栅极有一高电压输入时,场致反型器件首先导通,提供了静电的泄放回路,从而使MOS管的栅得到保护。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助